基于DSP和FPGA的视频编码器

目前,单一的CPU/DSP一般还不具备这样的计算能力。为了解决高清晰画面的实时视频压缩问题,本文提出了DSP和FPGA(Field Pro-grammable Gate Array)协同设计方案。使用FPGA完成视频采集、YUV(视频亮度Y、色度分量

UV)分离、数据I/O(Input/Output)等所有周边功能,使用高性能的DSP进行视频压缩编码,因而在视频编码器内DSP和FPGA能够进行流水操作,有效地提高了编码器的性能。

为了降低算法的计算复杂度,本文提出了基于宏块空间复杂度的宏块编码类型判别算法(MTJBSC)。在标准MPEG24视频运动估计算法中,判别宏块的编码类型是通过计算当前宏块内像素值方差和参考宏块与当前宏块之间的方差来实现的,因此计算量很大。MTJBSC算法首先计算出当前宏块的空间负责度(MBC),然后通过比较当前宏块的MBC与SAD(Sum of Absolute Difference)值来判断当前宏块的编码类型,大大降低了算法的计算复杂度。

1 硬件设计方案

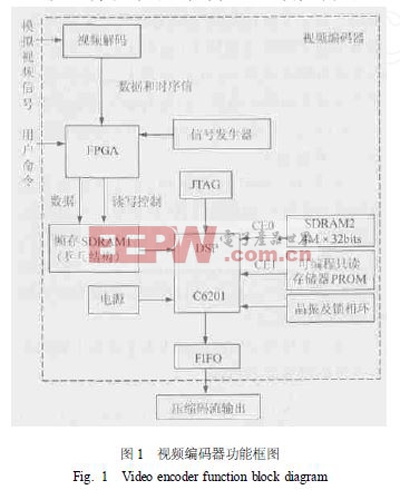

基于TI公司的图像开发工具包(Imaging Developer Kit,即IDK)[2]架构,设计了视频编码器的硬件平台。从整体上来讲,视频编码器的硬件实现由DSP和FPGA两个模块组成,其逻辑框图如图1所示。由于视频压缩编码计算量很大,为了尽可能提高视频压缩帧率,由DSP专门负责视频压缩编码,而视频采集、YUV转换和编码器I/O接口等其它功能则交由FPGA模块来实现。

如图1所示,用户控制命令(例如视频压缩模式)由FPGA模块首先截获,然后FPGA模块向DSP模块产生外部中断,DSP在响应中断时读取存储在FPGA中的用户控制命令字,然后DSP解析命令字,并根据用户要求的视频格式、帧图像分辨率和视频压缩码流速率进行视频压缩编码。

模拟视频信号经视频解码器转换为裸视频数据流,该数据流(或从数字摄像机直接获得的数据流)经FPGA预处理后送入帧存中。DSP读取帧存中的数据进行压缩编码,压缩后的视频数据送入FIFO中,最后FIFO中的数据通过串口送给信道编码器。

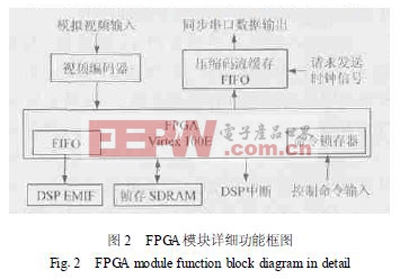

FPGA模块的逻辑框图见图2。如图2所示,视频解码器首先将模拟视频信号量化为复合的YUV数据,然后经FPGA进行YUV分离(和滤波)后送到帧存(图1中的SDRAM1)中,C6201使用DMA通道(异步方式)通过FPGA读取帧存中的YUV数据进行压缩编码。帧存(SDRAM1)在刷新(refresh)或缺页(pagemiss)时会引起DMA读等待,为了平滑这种等待引起的DMA读数据的抖动,设计时在FPGA的内部实现了一个高速FIFO。视频帧存采用了乒乓结构,将8M字节SDRAM分为两个4M字节的地址空间(每一个地址空间可以容纳一帧YUV视频数据(720×576×115字节)),一个地址空间用于存储当前正在采集的视频数据,另一个地址空间用于DSP的数据读取。在压缩CCIR601格式的视频图像(每秒25帧)时,由于DSP的处理速度(大约每秒10帧)慢于视频采集的速度,所以FPGA模块在采集完一帧数据进入等待状态,直到DSP压缩完上一帧视频数据时,这2个地址空间才进行互换。

DSP模块接收FPGA模块送过来的YUV视频数据,然后进行视频压缩编码,最后将压缩的码流再转交给FPGA模块,由FPGA模数据发送出去。DSP模块的存储单元(图1中的SDRAM2)用来存放参考帧数据和中间运算结构。MPEG-4压缩编码算法指令存放在PROM中,为缩短取指时间,编码器在启动时已将指令从PROM读到片内存储器中。MPEG压缩码流是变速码流(VBR),而当该码流在恒定速率(CBR)的信道上发送时,需要一个FIFO缓存来平滑编码器输出码率的波动。

该设计的特点主要表现在以下2个方面:

①可扩展性好。FPGA模块除了负责数据I/O功能外,还作为协处理器使用,可根据需要增加FPGA的门数来实现原来由DSP完成的功能,例如Huffman编码、运动估计等;

②灵活的视频压缩编码格式控制,编码器能够实时地根据用户的要求进行压缩编码。

2 视频压缩算法优化

(1)MPEG-4数据流优化设计

实验表明,如果代码和代码要访问的数据

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)