基于DSP+FPGA多通道单端/差分信号采集系统

在信号处理过程中,经常采用DSP+FPGA协同处理的方法。是因为DSP虽然可以实现较高速率的信号采集,但其指令更适于实现算法而不是逻辑控制,其外部接口的通用性较差。而FPGA时钟频率高、内部延时小,全部控制逻辑由硬件完成,速度快、效率高,适合于大数据量的传输控制,可以集成外围控制、译码和接口电路,在高速数据采集方面有着DSP以及单片机无法比拟的优势,但缺点是难以实现一些复杂的算法。因此,若采用DSP+FPGA协同处理的方法,便可以使DSP的高速处理能力与FPGA的高速、复杂的组合逻辑和时序逻辑控制能力相结合,达到互补,使系统发挥最佳性能。

在目前的信号采集及测试系统中,由于应用背景的复杂,经常需要对多路信号进行采集,有的甚至需要对多路单端及差分信号进行采集,在某些情况下,为测试分析的方便,还需要对采样率进行改变。文中介绍了一种采用DSP+FPGA协同处理的方法,并主要利用ADS8517这一A/D转换芯片来实现多路可以选择单端或差分输入的信号采集系统的设计方法。

1 系统实现功能

该系统可以实现32个通道单端信号或16个通道差分信号的采集输入,由DSP控制输入信号是单端信号还是差分信号,以及各自使能输入的通道,其中单端信号最多使能输入32个通道,差分信号最多使能输入16个通道。A/D在各个使能通道间采用类似时分复用的方法进行轮寻采样,A/D采样频率200 kHz,DSP可设置采样率分频值,对采样率进行改变,假如DSP设置采样分频值为D,使能输入通道数为N,则每个通道实际采样率为200 kHZ/(D·N)。

2 系统硬件设计

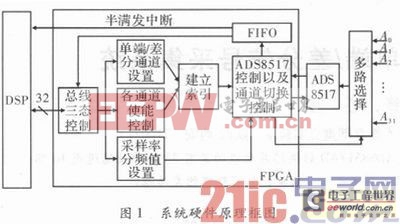

根据以上功能要求,整个系统的设计思路如图1所示。其中DSP采用TI公司的TMS3206713B,FPGA采用Altera公司的CycloneIII系列,A /D采用TI公司的ADS8517。ADS8517的主要性能:(1)16位分辨率;(2)采样频率:200 kHz;(3)模拟输入范围±10 V;(4)输出有串行和并行两种方式。

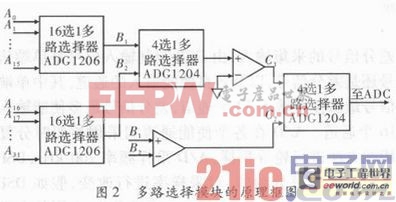

在整个系统中,FPGA根据DSP对各个通道是单端或者差分的设置,以及各个通道使能与否和采用率分频值的设置,控制ADS8517以及多路选择器,将A/D输入的数据以及其对应的通道存入一个FIFO中,当FIFO半满时向DSP发送中断,由DSP读取FIFO中A/D的采样数据及其对应的通道号。可以看出,设计重点主要集中在多路选择器的设计以及FPGA中硬件逻辑的设计。2.1 多路选择模块设计

2.2 FPGA部分的设计

由于DSP数据总线为32位双向总线,所以在FPGA中需要设计一个总线的三态控制器,来控制总线的输入输出,这部分设计较简单,模式相对固定,应用已成熟。

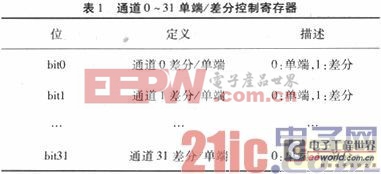

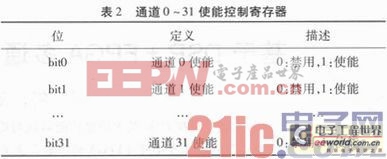

对于DSP发出的各个通道单端/差分控制,各个通道使能控制以及采样率分频值设置这些控制信息,由在FPGA中开辟出的3个32位寄存器来存储。通道单端/差分控制寄存器和通道使能寄存器的定义如表1和表2所示,采样率分频值设置寄存器中的32位无符号2进制整数表示相应的分频值。

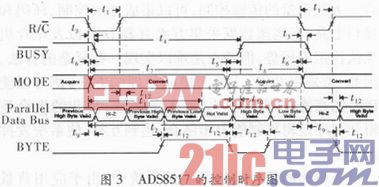

当DSP的控制信息设置好以后,根据通道单端/差分控制寄存器以及通道使能控制寄存器中的内容,建立一个使能通道索引表,索引表中字的个数等于使能的通道数,每一个字的字长为6位,依次将使能的通道号转换成二进制无符号数后放入表中各个字的低5位,每个字的高位记录相应的通道是单端还是差分,‘0’表示单端,‘1’表示差分。 设计采用ADS8517并行输出的工作模式,按照图3所示的并行输出方式时序图对其进行控制,其中 和BYTE信号为ADS8517的输入控制信号,

和BYTE信号为ADS8517的输入控制信号, 的下降沿表示一次采样的开始,

的下降沿表示一次采样的开始, 为高电平时表示可以读取A/D的输出数据,输出为并行8位输出,当BYTE信号为低电平时输出高8位,反之则输出低8位,从而完成16位分辨率的输出。

为高电平时表示可以读取A/D的输出数据,输出为并行8位输出,当BYTE信号为低电平时输出高8位,反之则输出低8位,从而完成16位分辨率的输出。 为ADS8517输出信号,为低电平时则表示本次A/D转换正在进行,为高电平时表示本次转换完成,因此当

为ADS8517输出信号,为低电平时则表示本次A/D转换正在进行,为高电平时表示本次转换完成,因此当 和

和 同时为高电平时,便可以读取本次A/D采样转换后的数据。

同时为高电平时,便可以读取本次A/D采样转换后的数据。

ADS8517控制以及通道切换控制模块在按照图3所示的时序控制过程中,要根据采样率分频值设置寄存器中的值控制两次采样之间的时间间隔,即控制两个相邻信号下降沿之间的时间间隔,从而改变采样率。在控制多路选择模块进行通道切换时,根据建立的索引列表依次切换通道,切换要在图3中两个相邻信号低脉冲之间进行,这样才能确保当A/D采样时,通道已经切换完毕,输入信号已稳定,从而保证采样的准确性。

除此之外,在FPGA中开辟一个字长为32位的FIFO,低16位存入A/D采样的数据,高16位存入该数据对应的通道号,FIFO半满,则给DSP发中断,由DSP将A/D采样后的数据读出,以便后续处理。要注意的是,FIFO深度不能设置得太浅,否则会很快达到半满,导致DSP对中断响应不过来。

3 结果验证

按照以上设计思路,完成硬件电路、FPGA内逻辑和DSP的程序设计,使用QuartusII中的在线逻辑分析仪SignalTapII Logic Analyzer对结果进行采样分析,图4所示为在DSP设置使能通道为30和31,并且均为单端的条件下采到的结果,与期望结果一致,类似这样通过多次改变控制条件采样分析发现,该系统可以正确地实现之前所描述的功能,从而验证了该设计的合理正确性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)