Altera SoC FPGA架构解析

产品,Altera设计其SoC FPGA时同时考虑了组件和系统成本。一片SoC FPGA的成本要比其替代的组件低50%,同时也能够降低系统成本。

当考虑SoC FPGA成本时,应重视三个关键方面:SoC中已经集成了多少等效功能? 应用需要高速收发器吗?如果需要,需要多少? 相关的电源供电成本有多大?

SoC FPGA解决方案的集成度有多高? 取决于应用,一片SoC FPGA会含有系统等效的处理器、所有外设、多个DSP、大量的片内存储器、高速收发器、时钟管理以及丰富的定制逻辑。不管怎样,都会有很多问题,如是否同时提供单核和双核处理器版本;除了ARM处理器内核,是否还集成了其他外设;硬核存储器控制器的数量;是否有集成锁相环(PLL);是否可以通过配置选项来降低成本;是否需要为控制器分配其他的FPGA逻辑;是否有公共封装引脚布局来优化平台成本等。

高速收发器是对设计成本有显著影响的另一关键特性。Altera SoC FPGA在全系列产品线上提供高速收发器选择。特别是,低端入门级器件以及容量最大的全功能器件都有高速收发器。高速收发器是PCIe等应用的关键因素。否则,会需要外部接口元器件,这增加了系统材料成本(BOM)。另一方面,某些嵌入式设计不一定需要高速收发器,Altera提供不含有高速收发器的SoC FPGA型号,从而降低了SoC FPGA元器件成本。

电源电压轨数量和容量对设计的成本和复杂度有非常明显的影响。所有SoC FPGA都需要多个电压轨,但是有的要比其他少很多。而且,某些SoC FPGA有严格的上电和关电顺序控制,要采用更复杂——而且昂贵的电源供电。特别是,由于可能会出现各种掉电条件,导致很难进行关电顺序。理想情况是,最好能够避免上电或者关电要求,特别是这些要求影响器件长期可靠性的时候。Altera SoC FPGA没有任何上电或者关电顺序要求。

4.电源

即使不是推动因素,低功耗也成为很多设计中越来越重要的因素。在SoC FPGA器件之间进行选择时,与功耗相关的重要因素有三个:集成、低功耗模式、上电/关电顺序要求。

通过集成降低功耗。如图4所示,在一片SoC FPGA中集成处理器和FPGA元器件能够把系统功耗降低10%到30%。I/O在器件之间传送信号,通常需要较高的电压,是应用中最耗能的组件。

图4.在一片SoC FPGA中集成处理器和FPGA减少了高功耗的芯片间I/O连接

低功耗模式。SoC FPGA具有各种低功耗和低成本特性。由于功耗的主要来源是器件的FPGA部分,因此,处理器系统和FPGA有分开独立的电源平面非常重要。为降低功耗,处理器可以通过软件控制将FPGA置于低功耗模式。

上电/关电顺序要求。为保证器件的可靠性,或者确保某种上电状态,硅片供应商会提出特殊的上电和关电顺序要求。上电顺序要求是很常见的,而通过关电规范来保护器件却很少见。这意味着,必须在电源上增加额外的电路,否则系统生产商会面临长期可靠性问题。

对于有关电顺序要求的器件,必须要非常小心,以避免每一电源轨失效,导致违反规范。这就要求采用比较模拟电路来监视电压轨,必须增加相应的保护电路。为保证正确的关电顺序,还需要有足够的功率存储。

Altera SoC FPGA内置了内部器件保护功能,因此,可以接受任意顺序的上电或者关电。Altera的确推荐了上电顺序,但只是作为系统电源供电设计人员的指南,帮助他们降低成本,并没有任何可靠性含义。其他SoC FPGA供应商的确有上电和关电顺序要求,如果经常违反,会导致器件的长期可靠性问题。

Altera SoC FPGA保证使I/O进入三态,避免了电路板级驱动竞争问题。如果违反了上电顺序要求,其他SoC FPGA供应商器件不能保证这些。

而且,Altera SoC FPGA支持“热插拔”,器件可以插入到已经上电的电路板中。其他SoC FPGA供应商并不提供这一功能。

5.未来发展路线图

选择新处理器体系结构是关键的决定。供应商的产品路线图能否满足未来应用需求,突出系统优势,长期看系统是否具有竞争优势,对此进行评估非常重要。考虑到较大的软件投入,基本软件能够轻松移植到未来产品上也非常重要。因此,不仅要知道SoC供应商在下一代产品上有哪些承诺,而且还要提出以下问题:

●在这一产品线上打算有多大规模的投入?

●今后对提高系统设计的竞争力会有多大帮助?

●工具有没有发展路线图?

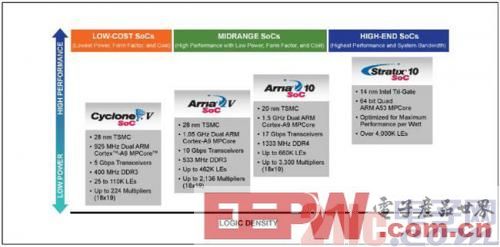

为满足SoC FPGA的目标应用需求(通信基础设施、工业、汽车、高性能计算、军事、航空航天、医疗、多功能打印机,等等),Altera制定了三代处理器发展路线图,如图5所示。

图5.Altera SoC FPGA系列产品发展路线图

发展路线图从28 nm Cyclone V和Arria V SoC FPGA开始。在20

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)