Altera SoC FPGA架构解析

据错误或者数据损坏的影响。

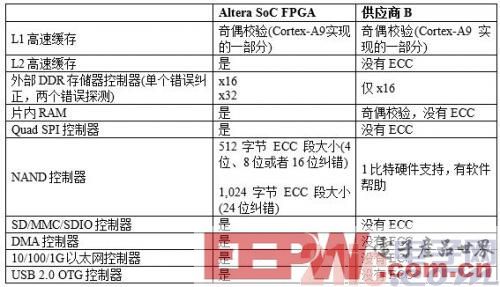

表1总结了Altera SoC的硬件ECC与其它厂家的对比

表1.SoC FPGA中的ECC

值得重点介绍的另一方面是NAND闪存。NAND闪存适用于文件系统存储,但有时候可靠性不如NOR闪存。因此,NAND闪存的ECC被用于消除错误。早期版本的NAND闪存控制器包括单比特ECC保护。这虽然有一些优点,但是CPU必须参与其中,CPU必须通过软件管理ECC,导致对性能有明显的影响。大部分现代NAND闪存控制器都包括多比特ECC保护。特别是,在Altera SoC FPGA中实现的NAND闪存控制器包括对512字节段的4比特、8比特和16比特硬件纠错,以及对1,024字节段的24比特硬件纠错。这实现了功能更强更需要的保护功能,而且不会降低性能。

存储器保护通常是先进的处理器具有的一种特性。不论是被称为存储器管理单元(MMU)还是存储器保护单元(MPU),处理器的存储器保护单元都能够防止错误或者非法的处理器会话读取或者损害其他的存储器区域。在Cortex-A9处理器中,ARM的TrustZone技术扩展了这一保护概念,为安全敏感的系统提供了系统级方法。

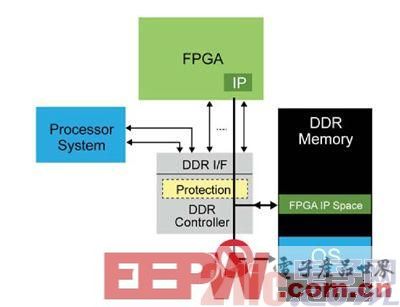

某些SoC FPGA将存储器保护扩展到了FPGA。为什么这一存储器保护来自FPGA,又用于FPGA呢?处理器和FPGA可以共享一个外部DDR存储器接口,以便降低成本,减小电路板空间,节省功耗。假设定制FPGA逻辑恰好覆写了一段属于处理器数据、应用程序代码,或者操作系统(OS)内核的存储器,那么会怎样呢?这会导致系统故障或者将处理器指向错误的方向。

为防止出现这种情况,为操作系统和嵌入式应用软件指定了特定的存储器区域,而其他存储器区域可以专门用于基于FPGA的功能,如图3所示。通过存储器保护,基于FPGA的功能不会损坏操作系统或者嵌入式软件区域。

图3.DDR存储器保护,处理器和FPGA共享公共的存储器。

看门狗定时器可以防止出错的软件将系统阻塞。在以前的双芯片分立方案,即处理器加FPGA的解决方案中,如果处理器运行出错导致看门狗复位,FPGA仍然能够运行。体系结构设计良好的SoC FPGA必须支持同样的“独立”行为,而且还提供选择给系统设计人员来决定是否重新配置FPGA。在很多情况下,很关键的是当处理器自己复位时,FPGA逻辑需要继续监视并响应外部激励。因此,在这种条件下,检查FPGA怎样重新配置非常重要。

如表2所示,Altera SoC支持处理器和FPGA的复位电路单独工作。由系统设计人员决定是否在CPU复位时重新配置FPGA。而其他SoC FPGA则在处理器复位时必须重新配置。

表2.SoC FPGA中的CPU复位

灵活性是很多设计人员选择使用FPGA的主要原因之一。可全面编程的SoC将设计灵活性扩展到了系统级。选择SoC FPGA时要考虑的三种体系结构:处理器启动和FPGA配置优先级可选、片内FPGA接口、封装引脚兼容。

处理器启动和FPGA配置的多种选择——对灵活性的需求首先从启动开始。SoC FPGA中有三种:“CPU最先启动”方式;或者先配置FPGA,再通过FPGA逻辑启动CPU方式;以及完全独立的处理器启动和FPGA配置机制的方式。目前,Altera SoC FPGA是唯一设计支持所有这三种选择的ARM Cortex-A9处理器SoC FPGA。

灵活性也扩展到片内FPGA接口上。有时候应用程序需要特性丰富的标准接口;有时候则要求简单或者可定制接口。对于需要高级功能的应用,SoC FPGA使用了ARM的AXI接口来连接处理器、硬核外设和FPGA逻辑。AXI标准使用成熟的业界标准,提供高速宽带接口。但是,对于不需要AXI所有特性的IP内核应该怎样呢?可扩展特性更重要,又会怎样呢?需求的一个极端可能是用户定制的1000线接口;而另一个极端则只需要一条线来点亮LED或者读取一个开关。

为满足这种变化的需求,除了AXI接口,Altera SoC FPGA还支持Avalon存储器映射(Avalon-MM)接口,以及Avalon流(Avalon-ST)接口。这些可扩展的Altera接口标准非常适合要求较低或者其他的特殊功能需求。这样,IP设计人员可以为每一功能选择最优接口。这也支持现有Altera FPGA客户继续使用现有的IP,不一定要移植到AXI。

封装引脚兼容布局进一步提高了设计、开发和实施阶段的灵活性。开发人员很容易在具有不同逻辑密度的器件之间移植设计,这些Altera SoC器件有相同的封装引脚布局。此外,开发人员可以在封装引脚兼容布局范围内,在具有收发器和不具有收发器的器件之间进行移植。为进一步降低成本,提供无收发器版本,它支持双核或者单核处理器。这些选择使得一个印刷电路板平台满足了不同的成本和特性应用。

3. 系统成本

目前发售的每一系统几乎都面临越来越高的成本压力。而SoC FPGA是具有先进特性的创新

- ALTERA FPGA在微处理器系统中的在应用配置(07-09)

- 藏在系统核心芯片中的DRAM控制器(12-10)

- 真实环境中的系统设计(09-09)

- IoT促进了低功耗的发展(12-05)

- 闪存革命无处不在(12-25)

- 悬崖边上的CPU设计师: 现在该往哪里去?(11-10)