一款基于FPGA和DDS的数字调制信号发生器设计

摘要:为了提高数字调制信号发生器的频率准确度和稳定度,并使其相关技术参数灵活可调,提出了基于FPGA和DDS技术的数字调制信号发生器设计方法。利用Matlab/Simulink、DSP Builder、QuartusⅡ3个工具软件,进行基本DDS建模,然后在DDS模块的基础上,通过单片机等电路组成的控制单元的逻辑控制作用,根据通信系统中数字调制方式的基本原理,设计并实现了数字调制信号发生器,从而实现二进制频移键控(2FSK)、二进制相移键控(2PSK)和二进制幅移键控(2ASK)3种基本的二进制数字调制。所得仿真结果表明设计方法的正确性和实用性。

关键词:数字调制信号;直接数字频率合成器;FPGA;DSP Builder

信号发生器种类很多,按是否利用频率合成技术来分,可分为非频率合成式信号发生器与频率合成式信号发生器。其中频率合成式信号发生器的频率准确度和稳定度都很高,且频率连续可调,是信号发生器的发展方向。频率合成技术发展很快,先后经历了:直接模拟频率合成技术、锁相频率合成技术(PLL)、直接数字式频率合成技术(DDS)和混合式频率合成技术。模拟频率合成的信号发生器电路硬件结构复杂,体积大,价格昂贵,不便于集成化;PLL易于集成化,体积小,结构简单,功耗低,价格低,而且具有极宽的频率范围和十分良好的寄生信号抑制特性,但频率切换时间相对较长,相位噪声较大;DDS是基于取样技术和数字计算技术来实现数字合成,产生所需频率的正弦信号,极易实现频率和相位控制,且切换时间快,尤其适于合成任意波形,集成度高,体积小,其因频率分辨率高、频率切换速度快、相位噪声低和频率稳定度高等优点而成为现代频率合成技术中的佼佼者。直接模拟式、锁相环式和直接数字式频率合成技术都有其优缺点,单独使用任何一种方法,有时也很难满足要求。此时可将这几种方法综合应用,即为混合式频率合成技术。而随着微电子技术和EDA技术的深入研究及发展,DDS技术更是得到了飞速的发展,同时,基于现场可编程逻辑门阵列(FPGA)的设计具有灵活、速度快等优点。因此,本文将基于DDS技术,应用Altera公司推出的DSP Builder和QuartusⅡ软件进行基本DDS建模,然后在DDS模块的基础上,通过单片机等电路组成的控制单元的逻辑控制作用,完成一个基于FPGA硬件平台的数字调制信号发生器的设计与实现。使其具有频率分辨率高、准确度和稳定度高、抗干扰能力强、相关技术参数灵活可调等优点。

1 DDS及数字调制方式的基本原理

1.1 DDS的基本原理

直接数字频率合成器(Direet Digital Frequencv Synthesizer-DDS)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。DDS频率合成器具有以下优良的性能:工作频率范围很宽;极高的频率分辨力;极短的频率转换时间;任意波形输出能力;数字调制性能好等。

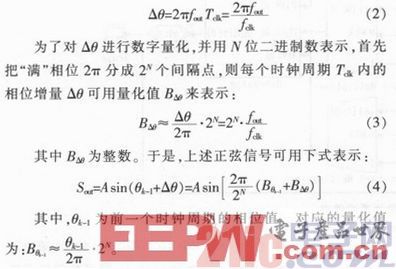

以合成正弦信号为例说明DDS的基本原理。对于一个正弦信号可表示如下:

Sout=Asin(ωt)=Asin(2πfoutt) (1)

其中:Sout为正弦信号,fout为正弦信号的频率。上式正弦信号表示对于时间t是连续的,为了用数字逻辑实现该表达式,需要进行离散化处理。用基准时钟进行fclk采样,令正弦信号的相位为:θ=2πfoutt,在一个基准时钟周期Tclk内,相位的变化量为:

由上所述,只要将相位的量化值进行累加运算,就可以得到正弦信号的当前相位值θk。其中用于累加的相位增量量化值B△θ决定了信号的输出频率fout,而且为简单的线性关系。这就是直接数字合成器DDS的设计原理。

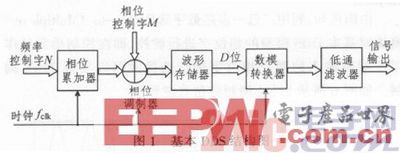

图1所示为一个基本的DDS结构,主要由相位累加器(PD)、相位调制器、正弦查找表(波形存储器ROM)、数模转换器(DAC)等构成。相位累加器是DDS的核心部件,其输入是相位增量B△θ,由于与输出频率fout成线性关系,故相位累加器的输入又可以称为频率字输入,事实上,当系统基准时钟频率fclk为2N时,B△θ就等于fout。相位累加器在基准时钟的作用下进行相位累加,当累加满时产生一次溢出,就完成一个周期的信号合成。

相位调制器接收相位累加器的相位输出,在这里加上一个相位偏移值,主要用于信号的相位调制,如PSK(相移键控),不使用时可以去掉该部分,或者加一个固定的相位字输入。

正弦查找表进行波形的相位到幅度的转换,它的输入是相位调制器的输出,也就是波形存储器的地址值,其输出送往数模转换器,转化成模拟信号,再经低通滤波器滤除其中的高频成分,将其变成光滑的正弦波输出。

由于相位调制器的输出数据位宽M也是波形存储器的地址位宽,由于受数模转换器位数的限制,因此在实

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)