基于DSP+FPGA的通用SSR信号处理机设计

才能不损失动态范围。并且相位的范围是[-π,π],补偿后相位必须归算到[-π,π].

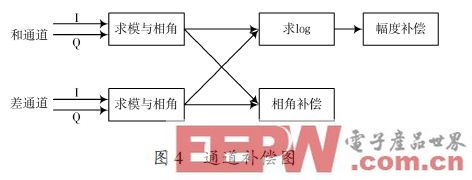

2.1.3 幅度与相角补偿

一般通道校正可以在射频补偿,也可在I,Q通道补偿,但都是复数乘法补偿,必然有舍入损失。这里插入了log模块,将乘法简化为加法,因此直接在求模与相角后补偿相角,并在求log后补偿幅度。这样将乘性误差转化为加性误差,补偿精度比直接在I,Q通道补偿高很多,如图4所示。

2.1.4 AC通道处理

AC通道在边沿检测、脉冲预处理、框架检测后提取AC码参数,并且进行去除幻影处理。幻影框架是因为不同框架脉冲交叠在一起,产生多个虚假的框架,从而产生多个虚假的应答,必须去除。

单脉冲二次雷达目标信号处理去除幻影的基本思路是利用单脉冲二次雷达和、差通道的信号幅度信息来去除幻影框架。属于同一框架脉冲的AMP 值应具有一致性,不具有AMP 一致性的两个脉冲很可能属于不同的框架。并且通过以下步骤去除幻影:

(1)可能的幻影框架判定

根据完全重叠的定义,对所有收到框架中的F1和F2脉冲进行完全重叠判定。通过判断该F1,F2脉冲是否在另一个框架的F1后n ×29±3( n = 0,1,…,14)的位置上(系统时钟选20 MHz)。即计算两个脉冲的距离值差,如果等于n ×29±3(n = 0,1,…,14),即为可能的幻影框架。

(2)构成交叠关系的框架

根据构成交叠关系的框架的定义,对于上步找到的n 个可能的幻影框架,找出与每个框架Ai(1≤ i n )构成交叠关系的所有框架,即计算两个框架的距离值差,如果等于n ×29±3( n =0,1,…,14),就是构成交叠关系的框架,假定有m 个构成交叠的框架。

(3)去除幻影

根据判定幻影框架充分必要条件中的Σ,Δ值均具有一致性的原则,分别计算出每一个可能幻影框架Ai(1≤ i ≤ n )的参考信号的Σ 值,跟每个与之构成交叠关系的框架Bi((1≤ i ≤ m )的参考信号的Σ 值之差,同时也计算出两者的Δ 值之差。只要其中有一组的Σ 值之差具有一致性,且Δ 值之差也具有一致性,就将该框架作为幻影删除。

这里去幻影是流水处理,为了处理方便将此算法放在FPGA内处理。

2.1.5 S通道处理

S通道经过边沿检测,报头检测,计算参考值,DF认证,重触发,参数提取模块完成S模式应答信号的检测与提取[6-7].

S 模式信号报头为8 μs,并且数据可长达112 μs,提取电路相对复杂。这里采用移位寄存器来提取码值。即检测到有效报头后,等数据脉冲部分到来后,再启动数据提取,将数据逐次打入。

2.2 编码主要流程及功能

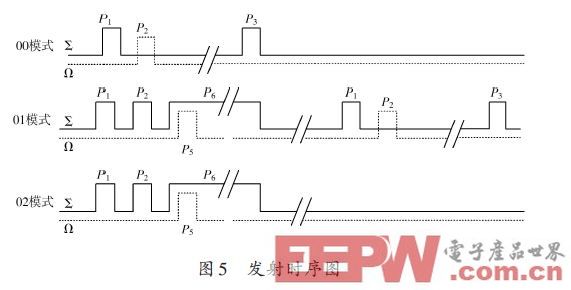

信号处理机还须进行编码发射时序处理,发射时序如图5 所示。根据图3 流程,航迹计算机来配置每一SCAN 的发射模式及参数表。信号处理机来顺序读取每个脉冲的模式及相应参数,并据此来控制发射波形。

这里模式仅分为三种,分别是00、01、02.如图5所示,00 模式是AC 模式,即AC 交替模式,用于发射AC码。01 模式是S 和AC 联合全呼叫模式,这样装有S 模式和只装AC 模式的飞机都能应答。02 模式是点名呼叫模式,这样地址一致的S模式飞机才响应并应答。

2.3 点迹处理

信号处理机同时完成点迹处理,即将飞机的多个应答处理为一个点迹报告,并传送到航迹计算机,这部分任务由DSP完成。

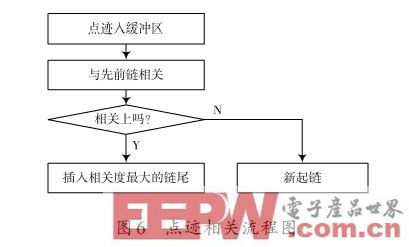

点迹处理处理分点迹相关和点迹凝聚的两个过程。其中点迹相关的基本流程如图6所示。

相关上的点迹形成一个链,码值的凝聚则根据链上所有应答的置信度来凝聚码值,生成距离、方位、点迹质量、紧急/识别标注等,然后生成点迹报告送至航迹计算机。

3 结论

本系统采用FPGA+DSP的方式设计、实现了单脉冲二次监视雷达实时信号处理机,结构清晰简单,功能强大,成本相对较低。经测试SSR信号处理机,可以达到≤15 m级的距离分辨率。并且根据二次雷达设备规范[8],每个SCAN 可以达到约600个目标,或每个扇区可处理64批目标,检测概率大于99%,测角精度优于0.05°。同时系统有BIT 功能,可以离线或在线检测,可靠性很高。另外,系统简单扩展既可以实现1、2、B、D、IFF等功能。综上所述,本二次雷达信号处理机具有较高的性价比,市场前景广阔。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)