基于FPGA的软件无线电高速数字信号处理

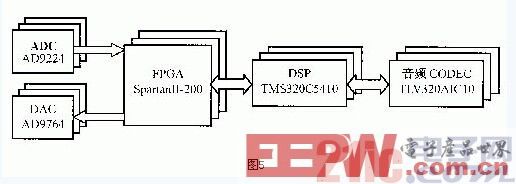

数字化收发信机,硬件设计如图5所示。

如图5所示,中频A/D、D/A分别采用AD公司的AD9224和AD9764,其中AD9224分辨率为 12bit,AD9764为14 bit,采样速率为30.720MHz;DSP选用TI公司的0芯片,最高处理速度为100MIPS;音频A/D、D/A由 TLV320AIC10实现。FPGA选用Xilinx公司的SpartanII-200,规模为20万门,最高工作频率为200MHz,该芯片主要完成抽取率为512的DDC功能和插值率同样为512的DUC功能,而且是在同一片FPGA中实现。FPGA单元与DSP接口的数据速率为60kHz。 FPGA开发工具为Xilinx Foundation3.1,编程语言采用VHDL和Schematic混合设计方法,并利用CORE Generator提供的DA FIR滤波器方便地实现半带滤波器和整形高阶FIR滤波器功能。

5 结束语

本文在建立单信道软件无线电数学模型的基础上,深入研究了FPGA技术在软件无线电高速数字信号处理中的应用,特别是在DDC和DUC中的应用。研究表明,这种基于FPGA/通用DSP的协同设计方法,无论是在性能价格上,还是在设计的灵活性上,都有很大的优势,非常适合目前软件无线电硬件平台设计。

参考文献

1 Mitola J. The software radio architecture. IEEE Communication Magazine,1995(5)

2 Cummings M, Haruyama. FPGA in the software radio. IEEE Communications Magazine, 1999,37(2)

3 R.E.克劳切,L.R拉宾纳.多抽样率数字信号处理.北京:人民邮电出版社,1988

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于现场总线的可重构数控系统的研究(12-20)

- 基于Verilog的多路相干DDS信号源设计(10-15)

- 基于DSP和FPGA的一种新型光伏并网控制方法(12-13)

- Linux + Firefox 登陆网上银行(04-21)

- 对Linux内核中进程上下文和中断上下文的理解(04-27)