基于FPGA的软件无线电高速数字信号处理

后经过低通滤波和多级抽取滤波,降低信息的采样速率,由 FPGA送至通用DSP,实现基带信号的调制解调;对于数字上变频结构,和下变频有完全对称的结构,所以分析时仅以接收机为例。

4.1 本地频率产生器和混频器

DDC结构中第一个环节就是要实现本地数字混频,主要由两个部件完成,一是乘法器,二是数控振荡器(NCO)。乘法器是数字信号处理中的基本运算单元,在FPGA中设计较为复杂,而且占用资源也比较多,但在具体实现FIR滤波时,往往不采用这种直接的乘累加的形式,以免占用大量的资源;在实现混频时,由于只需两个乘法器,而且是在很高的速率下进行,所以不考虑资源的限制。在Xilinx公司FPGA产品中,有的已在芯片内部嵌入了乘法器,这种内置乘法器充分结合了芯片硬件特点,使得运算速度更高。

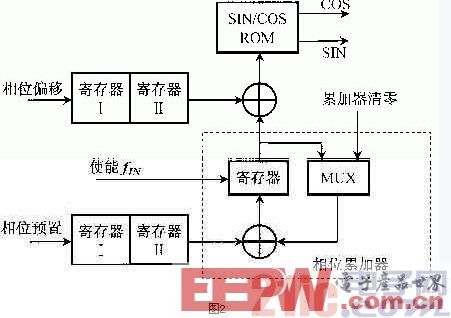

NCO的硬件结构如图2所示,主要由相位累加器和SIN/COS表构成。相位累加器产生的相位作为地址去查找ROM表,查到的SIN/COS值即本地载波的数字频率送至乘法器,完成混频。在实现NCO时有以下参数值得注意:

· NCO产生数字频率的精度。此参数与SIN/COS 值的位数有关,位数越宽,则精度也就越高,但占用FPGA的资源也就越多。

· 载波的同步。如果需要本地载波做到严格的同步,则需要额外的锁相环结构获取偏移相位,进行调整。

· NCO输出频率的噪声。噪声的产生与频率在时间上量化有关,由于采样时刻不一定严格对齐载波的相位,所以会产生噪声,但构造更大的正弦或余弦表会减少噪声分量,这同样会增加FPGA的资源占用。

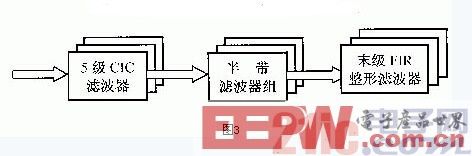

4.2 抽样率变换滤波器组

下变频过程中经过混频后的信号必须进行抽取滤波,以便降低抽样速率,使得通用的DSP对基带信号处理时有充足的时间完成运算;同样,在上变频过程中,首先要进行插值滤波,提高抽样速率,从而实现在IF范围内频谱的搬移。根据DDC总抽取因子的大小,我们把数字下变频分为两类:即当抽取率大于32时,认为是窄带下变频,反之则认为是宽带下变频。无论是宽带还是窄带,一般都采用FIR结构实现抽取滤波器,但对于窄带下变频,由于抽取因子较大,所以其抽取滤波器组也更为复杂一些。参考古得曼(Goodman)和开莱(Carey)提出的设计多级抽取器和内插器的经典模型[3],对窄带下变频作如图3设计,其中CIC滤波器为整系数滤波器,滤波时无需乘法运算,而半带滤波器有一半系数为零,这样在滤波时大大减少了计算量。

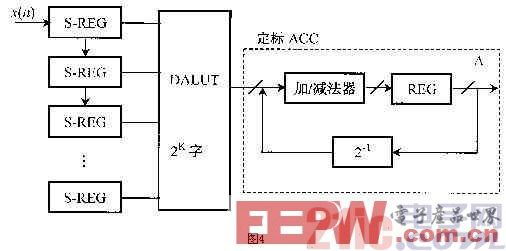

实现FIR滤波功能的基本元素包括乘法器、加法器、延迟单元以及存储单元等,其中乘法器的设计最为复杂。用 FPGA技术作乘累加运算通常有移位相加、加法器树、查询表和逻辑树等设计方法,不管采取哪种方法,要实现一个高阶的数字滤波器都将占用相当大的资源。相比较来说,采用分布式运算DA算法(Distributed Arithmetic)的FPGA设计无论是在逻辑资源占用上,还是处理速度上都具有很大的优势,特别是对于基于SRAM结构的FPGA更加适合于DSP 功能的设计。有关DA算法早期比较著名的阐述,是在1974年由Abraham Peled 和Bede Liu在讨论数字IIR滤波器和FIR滤波器硬件设计时涉及到,1975年在IEEE Proceedings中Freeny发表了一篇关于DA算法在贝尔实验室电话系统中应用的论文,同时惠普公司的Kai-Ping Yiu提供了一种有关符号位的DA设计方法;此后,西门子H.Schroder以及RICE大学C. S. Burrus 在提高算法的处理速度方面做了深入的研究。随着大规模集成电路技术的发展,特别是可编程逻辑器件的发展,DA算法在数字滤波器硬件设计中的研究进一步加强,SDA(串行DA)算法和PDA(并行DA)算法已成为FPGA实现DSP功能最为有效的方法。根据DA算法设计的思想,我们进行FIR滤波器设计如图4所示。

图4为FIR滤波器实现的串行DA形式,其中S-REG为串行移位寄存器,实现输入数据的并/串转换,并由 TSB(Time-Skew Buffer)完成数据的移位缓存,产生访问DALUT的地址;查表后得到的输 出数据由定标ACC单元完成累加,累加的结果即为滤波后的值。SDA算法处理的速度与抽头系数的大小无关,只与输入信号的数据位数有关,例如当x(n) 的数据宽度为12bit,则需要12个时钟来完成一个输出结果的运算。PDA(并行DA)算法可相应提高信号处理的速度,但它是以牺牲更大的逻辑单元为代价的。为了实现较高性能的滤波器指标,往往需要很多个抽头,这时DALUT必然会占用很大的空间,如每增加一个抽头,DALUT的容量就会增加一倍 (2K),在实际处理时,通常采用分解级联的方法,利用多个DALUT实现总的滤波功能。

4.3 FPGA实现和实验结果

我们设计了一个中频为10.75MHz,带宽为20kHz的中频

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于现场总线的可重构数控系统的研究(12-20)

- 基于Verilog的多路相干DDS信号源设计(10-15)

- 基于DSP和FPGA的一种新型光伏并网控制方法(12-13)

- Linux + Firefox 登陆网上银行(04-21)

- 对Linux内核中进程上下文和中断上下文的理解(04-27)