基于FPGA的软件无线电高速数字信号处理

摘 要 本文首先建立了单信道的软件无线电数学模型,分析比较了FPGA、ASIC以及DSP设计方式的优缺点,并深入研究了FPGA技术在软件无线电中的应用。

关键词 现场可编程门阵列 上/下变频器 DA算法

1 引言

软件无线电的基本思想是:A/D、D/A变换器尽可能地接近天线,用软件来完成尽可能多的无线电台的功能1软件无线电的结构大致分为三种:射频低通采样数字化结构、射频带通采样数字化结构和宽带中频采样数字化结构。

对于前两种方式,由于是对射频信号直接进行采样,结构简洁,并把模拟电路部分减小到最低限度,无疑是最理想的方式,但这种结构不仅对A/D转换器的性能如转换速率、工作带宽、动态范围提出了非常高的要求,同时对后续DSP或ASIC的处理速度要求过高,以至于无法实现;宽带中频采样的软件无线电结构与目前的中频数字化接收机(发射机)的结构是类似的,都采用了多次混频体制,在适当的中频位置进行数字化,所以它是三种结构中最容易实现的,对器件的要求也较低,但它离理想软件无线电的要求仍有一定距离。

2 单信道软件无线电数学模型

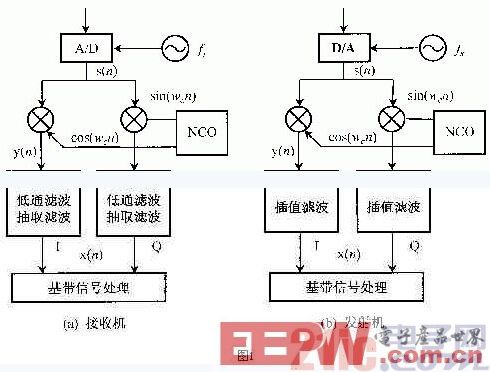

单信道软件无线电接收机和发射机的数学模型如图1所示。以接收机为例,将数字处理流程分为两部分:一是数字下变频部分,包含NCO、混频器、低通滤波以及抽取滤波器;二是基带信号处理部分,包含解调、译码、自适应均衡、帧调整、比特调整和链路去加密等算法。数字下变频单元的功能一是进行频谱搬移,将射频信号或中频信号转换为零中频信号;二是降低采样速率,将满足射频或中频采样定理的高速采样信号降低为低速基带采样信号。

就目前器件的发展水平,要想实现完全的射频数字化,几乎还不太可能,所以研究的重点往往放在中频数字化上。根据上面的分析,中频数字化中基带信号处理部分由于处在较低速率上,一般采用通用DSP方案实现,通过软件来实现各种功能;而对于数字变频部分,它们过高的速率使得通用DSP无能为力,即使像运算速度已高达600 MHz的TMS320C64X也不能解决数字中频的处理,所以,如何解决A/D采样后高速信号的处理,依然是中频以下软件无线电的关键。目前,人们已经提出了一些解决关键元器件的方法,并已出现了大量的数字中频产品,尤以Harris公司和Gray公司为代表,像Harris公司的可编程数字上/下变频器 HSP50415、HSP50216等都为软件无线电的实现奠定了良好的基础。同时,在另一方面,由于FPGA技术的迅速发展,超大规模、高速度的 FPGA芯片不断出现,特别是像Xilinx公司的SpartanII、VirtexII具有独特的快速逻辑进位、DDL功能,为实现高速数字信号处理提供了可能,这种FPGA加DSP的设计方法为实现软件无线电提供了一种更加灵活的方案,本文的重点正是研究FPGA技术在软件无线电中的应用。

3 几种技术方案的比较

3.1 FPGA的发展现状

FPGA(Field Programmable Gate Array)现场可编程门阵列是最近10年发展起来的新型可编程逻辑器件。由于FPGA器件的功能由逻辑结构的配置数据决定,工作前需要从芯片外部加载配置数据。配置数据存储在片外的EPROM或其它存储体上,人们可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场编程。FPGA与CPLD一起在数字电路中发挥着巨大的作用。FPGA技术的发展可以从全球最大的FPGA生产厂商Xillinx公司推出的产品看出,无论是在规模、处理速度还是功耗上,都得到了长足的进步,如VirtexII系列XC2V10000:系统逻辑门为10M,内含专用18(18位乘法器192个,并有Block RAM 3456kbit,内部时钟处理速度为420MHz,IO数据速率可达840Mbit/s,核心电压1.5V。

3.2 FPGA与ASIC的比较

下面我们从功耗、体积、成本、现场可编程性以及硅芯片的解决方案等角度分别对高速DSP、ASIC以及FPGA设计方案进行比较,如表1所示。

从表1中可以看出,与ASIC设计方案比较,FPGA具有更大的灵活性。ASIC设计是通过在FPGA中的模型来测量,当接近要求时,再转到小批量ASIC 中测量,这种测量是需要反复进行的。设计系统直接使用可重构的FPGA,不但增加了设计的灵活性,而且大大减少了投放市场所需的时间。

3.3 FPGA与DSP的比较

DSP芯片在市场上已有20几年了,其性能也在不断地提高,但要达到千兆赫量级的时钟速度所要求的功耗仍然较高,并且其串行处理的结构不可能实现高阶的数字滤波器功能(如表2所示)。

4 FPGA在数字中频处理中的应用

根据图1所示数学模型,FPGA在软件无线电中的应用主要体现在数字上变频DUC和数字下变频DDC中。经过 A/D采样后的信息直接送给FPGA,在FPGA中完成本地混频,把中频信号搬移到基带信号,然

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于现场总线的可重构数控系统的研究(12-20)

- 基于Verilog的多路相干DDS信号源设计(10-15)

- 基于DSP和FPGA的一种新型光伏并网控制方法(12-13)

- Linux + Firefox 登陆网上银行(04-21)

- 对Linux内核中进程上下文和中断上下文的理解(04-27)