基于Nios II的视频运动目标检测跟踪系统设计

摘要:文章是以Nios II处理器为中心的视频运动目标检测跟踪系统,通过CMOS图像传感器采集视频图像信息,采用帧间差分法检测运动目标,形心跟踪算法对目标进行跟踪,最后在VGA显示器上显示视频中运动物体。实验结果表明,该系统可达到运动目标检测跟踪的理想结果。

0 引言

运动目标检测跟踪就是将运动的目标从视频图像序列中检测出来,对其进行跟踪。在计算机视觉领域和智能视频监控系统中,目标检测与跟踪系统是一个最要的研究内容,该系统在很多领域中经得到广泛的应用,例如在家庭住宅小区、智能交通、银行、超市等场所都设有视频监控系统,起到了不需要人为的作用,就可以对采集来的视频图像信号进行处理,并对监控系统进行控制。视频监控与监视系统VSAM是由美国国防部研制出来的,其作用是对整个场景进行监控,该系统可以自动地调多个图像传感器无缝接入,主要应用在战争、危险场合的监控。马里兰大学研制出的W4实时监控可以在夜晚或者光线较差的环境下对出现的人定位和分割,主要应用在智能交通、家居服务等。视频运动目标检测与跟踪系统对检测目标的准确性和实时性要求很高。SOPC是嵌入式微处理器可编程片上系统,可在FPGA芯片上实现。本文采用SOPC(在FPGA嵌入NiosII软核)作为视频处理核心器件的方案,与传统的采用DSP和ARM芯片的方案相比,具有成本更低、设计更灵活,而且能达到软硬件协同工作、处理速度更快、容易升级。系统采用Altera公司的CycloneII EP2C35F672C6作为核心处理芯片,NIOSII软核处理器为核心对运动目标实时准确地检测与跟踪。

1 系统组成及框图

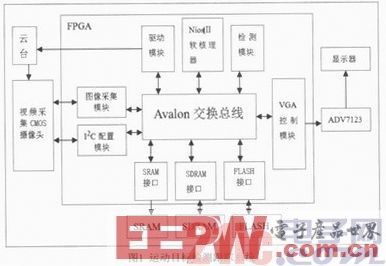

本文是基于FPGA的视频运动目标检测跟踪系统,主要分为四个模块:图像采集模块、存储模块、目标检测跟踪模块和VGA显示模块。

1.1 图像采集模块

图像采集模块的作用是接收CMOS图像传感器采集到的视频图像。本系统采用的是友晶公司提供的TRDB—D5M摄像头开发套件,使用的是CMOS图像传感器,它是将光学图像转化成电子信号的有源像素传感器,是利用CMOS半导体而制成的。TRDB—D5M作为一款摄像头套件,有很多摄像方面的优势;高帧率、优秀的低亮度性能、微弱的暗电流、全局复位解除(使所有像素点同时开始曝光)、可编程控制帧率、帧规模、曝光时间,片上锁相环、自动黑面校准等。

1.2 存储模块

本设计在硬件系统中使用一片SDRAM作为图片缓存的存储器,在软件系统中,备用一片SDRAM存储帧图片,使用一片SRAM存储软件代码和软件处理过程的中间数据。

1.3 目标检测跟踪模块

系统中大部分模块是由Verilog HDL设计的,使用硬件来完成实际的功能,此模块是在基于NiosII IDE集成开发工具使用C语言实现的,我们在EP2C35中嵌入NIOS II软核,控制连接在外部总线上的SDRAM和SRAM。在整个模块中,FPGA是综合了NIOS II处理器、SDRAM控制器、SRAM控制器、摄像头等许多模块的最主要的部分。

1.4 VGA显示模块

VGA输出接口芯片采用的是美国AD公司的ADV7123,它是一款单芯片包含3路高速、10位输入的视频D/A转换器、行场同步信号、行场消隐信号、时钟信号。ADV7123对RGB视频数字信号进行D/A变换成VGA需要的RGB模拟信号。最后将运动目标检测跟踪结果显示到PC显示器上。运动目标检测跟踪系统的总体框图如图1所示。

运动目标检测是目标跟踪的前提,其作用就是当视频图像序列中有运动目标出现,通过检测算法将目标从背景图像中提取出来。根据监控场景是运动的还是固定的,可以分为背景是固定的运动目标检测和背景是运动的运动目标检测。本系统是对背景运动的运动目标检测,目前,运动目标检测主要有三种方法:背景差分法、光流法和帧间差分法。背景差分法和光流法与帧间差分法相比,具有精度高定位准的优点,但算法的复杂性较高,难以在硬件平台上实现实时处理,因此,本系统采用的是帧间差分法。

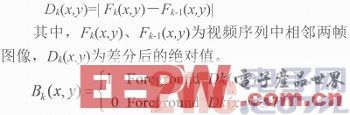

帧间差分法是对连续视频序列图像中相邻两帧作差,从而得到运动目标的方法。通常选取相邻的两帧或三帧图像进行差分运算,设t时刻当前帧图像为Fk(x,y),t-1时刻的前一帧图像为Fk-1(x,y),两帧进行相减运算如下:

其中,T为阈值,如果相邻两帧差分后的像素灰度值大于T,则二值化图像Bk(x,y)像素点为1表示运动目标区域,若为0表示背景区域。帧间差分算法基本流程如图2所示。

1.5 目标跟踪

目标跟踪有很多算法,本系统选用的是形心跟踪法。形心就是运动目标的中心,对于准确定位出目标具有重要的意义。本文形心的获取主要是通过帧间差分法检测到运动目标后,对检测到的所有动态点横坐标和纵坐标进行统计,然后算

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)