基于USB和CMOS图像传感器的指纹识别仪设计

引 言

CMOS图像传感器是近年来得到快速发展的一种新型固态图像传感器。它将图像传感部分和控制电路高度集成在同一芯片里,体积明显减小、功耗也大大降低,满足了对高度小型化、低功耗成像系统的要求。与传统的CCD图像传感器相比,CMOS图像传感器还具有集成度高、控制简单、价格低廉等诸多优点。因此随着CMOS集成电路工艺的不断进步和完善,CMOS图像传感器已经广泛应用于各种通用图像采集系统中。同时作为一种PC机与外围设备间的高速通信接口,USB具有许多突出的有点: 连接简便,可热插拔,无需定位及运行安装程序,无需连接外设时关机及重启系统,实现真正的即插即用;高传输速率,USB1.1协议支持12Mb/s;不占用系统硬件资源,能够自动检测和配置外围设备,不存在硬件冲突问题。

因此,利用CMOS数字图像传感器与USB接口数据传输来实现的指纹识别仪具有结构简单,体积小,便携化等优点。现将介绍利用OMniVision公司的CMOS彩色数字图像传感器OV762M和cypress公司的EZ—USB AN2131QC USB控制传输芯片(内部集成了增强形51内核)来实现指纹信息的采集和USB传输,同时由于指纹传感器输出数据的速率(27MB/s)与USB控制器(AN2131QC)数据传输速率(12Mb/s)的不匹配,故系统采用了SRAM和CPLD构成中间高速缓冲区。

系统结构

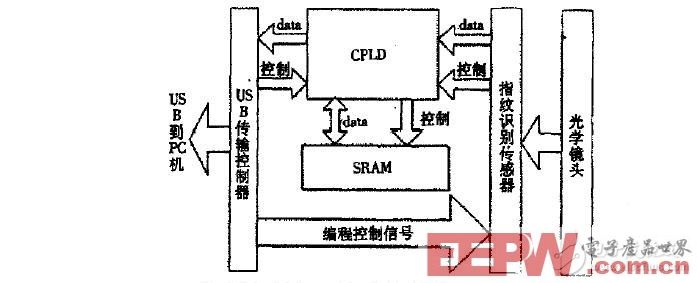

应用AN2131QC、CPLD和OV762M设计的指纹识别系统硬件框图如图1所示:

?

图1 指纹识别硬件系统简略框架图

首先,AN2131QC通过I2C对指纹识别传感器(OV7620)的窗口设置等参数进行配置,光学透镜把像成在OV762M的像面上后,CMOS图像传感器(OV7620)对其进行空间采样,并按照一定的帧频连续输出8位的数字图像数据Y[7∶M](输出数字图像数据的帧同步信号为VSYNC,水平有效信号为HREF,输出时钟信号为PCLK)。为了实现指纹传感器输出数据与USB控制器(AN2131QC)读取数据速度与时序的匹配,使用了SRAM(IS61C1024)和CPLD构成高速缓冲区,利用此高速缓冲区将OV762M采集的指纹数据缓存。最后AN2131QC实现与上位机的USB通信,将高速缓冲区中数据的传输到PC机进行相应图像处理。

CMOS数字图像传感器OV7620

CMOS数字图像传感器OV762M集成了一个664×492 的感光阵列、帧(行)控制电路、视频时序产生电路、模拟信号处理电路、A/D转换电路、数字信号输出电路及寄存器I2C编程接口。感光阵列得到原始的彩色图像信号后,模拟处理电路完成诸如颜色分离与均衡、增益控制、gamMA校正、白电平调整等主要的信号处理工作,最后可根据需要输出多种标准的视频信号。视频时序产生电路用于产生行同步、场同步、混合视频同步等多种同步信号和像素时钟等多种内部时钟信号,外部控制器可通过I2C总线接口设置或读取OV762M的工作状态、工作方式以及数据的输出格式等。

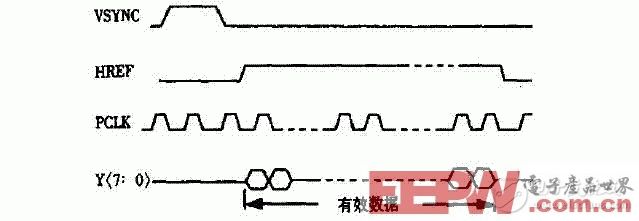

AN2131QC通过I2C总线接口设定OV762M的寄存器来控制输出帧率在0.5帧/s~3M帧/s之间变化,输出窗口在4×2~664×492 之间可调(默认输出640×48M的标准VGA格式),设置黑白平衡等。根据指纹采集的需要,窗口输出设置为: 320×288,经过设定后的OV762M输出时序如图2 所示:

?

图2 0V762M输出时序

VSYNC是垂直场同步信号(也是每帧同步信号,CMOS是按列采集图像的),其下降沿表示一帧图像的开始,HREF 提供了一种有效的控制方式,当输出像素行列分别处于设定窗口之间时HREF 为有效高电平,此时输出有效的视频数据,PCLK是输出数据同步信号,上升沿输出一个有效的像素Y[7∶M]。

基于CPLD技术的高速数据缓冲区的实现

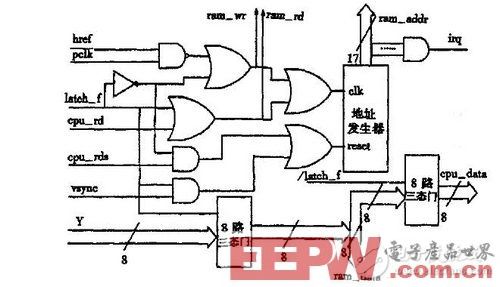

在由CPLD和SRAM构成的高速数据缓冲区中,CPLD充当了SRAM的控制器,其内部电路实现框图如图3所示:

?

图3 SRAM高速缓冲区控制器的CPLD实现

图3中ram_rd,raM_wr为输出到SRAM的读写信号线,raM_data,ram_addr为SRAM的数据地址总线;latch_f为SRAM的读写允许信号,当为高电平时允许对SRAM写操作,为低电平时允许对SRAM读操作;两个8路三态门用于隔离总线,当对SRAM写时,输出cpu_datA为高阻态,当对SRAM读时,将采集数据信号Y [7∶M]隔离;cpu_rds,vsync为开始读写信号,单个正脉冲将SRAM地址置0;cpu_rD作为SRAM快速读脉冲,pclk为SRAM写脉冲;irq为写满标志,用于向上提供中断标志;地址发生器用于产生SRAM地址(IS61C1024有17根地址线)。

?

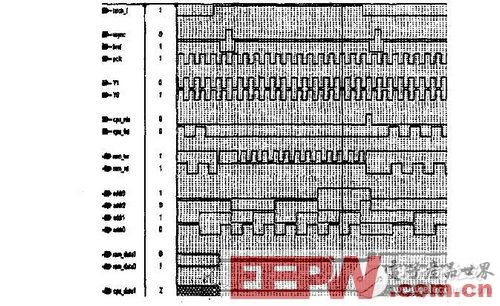

图4 CPLD实现的仿真波形

由图3中逻辑知道,当允许对SRAM写(latch_f=1)且采集的数据有效(href=1)时,pclk脉冲通过地址发生器产生地址(sync单个正脉冲将SRAM地址复位到0),将采集的数据Y[7∶M]写入SRAM中,当写满(写完一帧的32M像素×288像素)时,irq信号有效,通过中断将latch_f置低允许将

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)