一种于FPGA的高速导航解算系统设计与实现

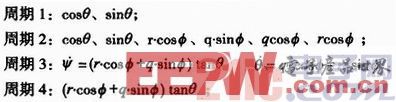

块对数据进行并行处理,不同计算周期所计算的算子安排如下所示:

2.3 位置信息并行解算的FPGA设计

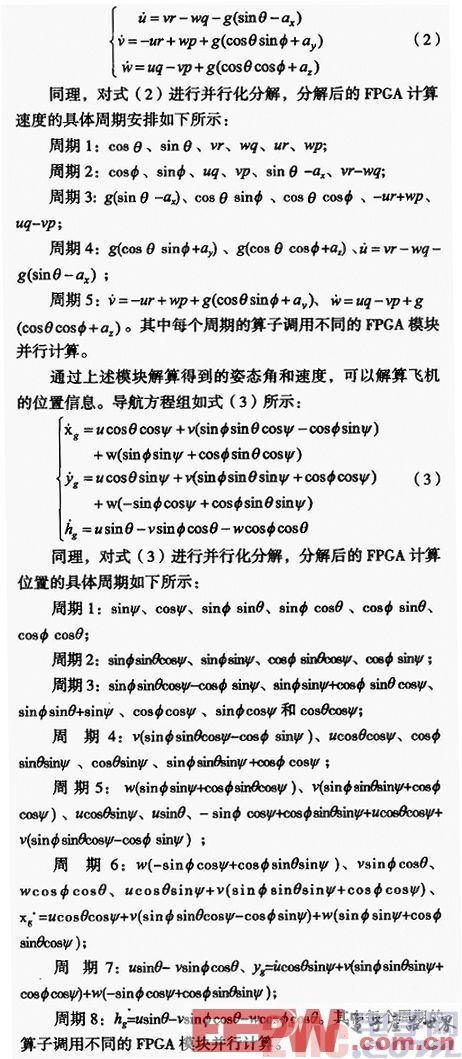

通过传感器获得的加速度以及上述模块解算的姿态角可以解算飞机三轴速度,飞机速度解算方程如式(2)所示。

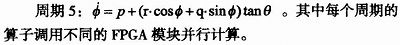

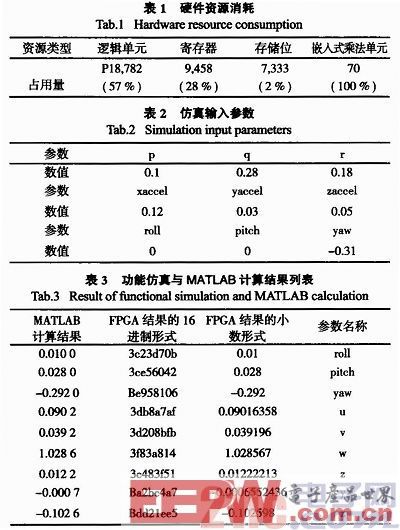

依据上述并行计算结构进行硬件描述语言的编程和编译,导航解算系统所占用的FPCA硬件资源如表1所示。

图2为导航解算FPGA功能仿真时序图,以此估算模块计算所消耗的时间。一次姿态解算需要230个时钟周期,一次导航解算需要980个时钟周期,那么在50 MHz的系统时钟下,姿态解算需时4.7微秒,导航解算需时20微秒。导航解算系统功能仿真结果与计算机计算结果进行对比,仿真步长为0.1秒,仿真输入参数如表2所示,计算结果如表3所示,通过比对可以发现,FPGA的计算结果与MATLAB计算结果没有偏差,说明导航解算系统能够正确地进行导航信息的解算。

3 实验结果与误差分析

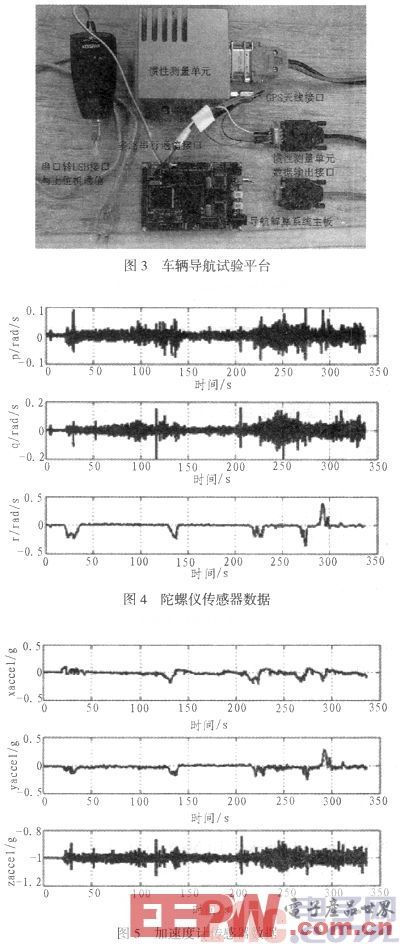

在一辆普通轿车上进行导航实验,系统的搭建如图1和图3所示。系统的核心是一块承担数据处理任务的FPGA,在芯片外接合适的IMU,IMU的功耗和体积基本决定了导航系统的功耗和体积。所以整个导航系统的结构是简单和小巧的而且节能的。

实验进行了340秒,如图4和图5所示,依次是三轴陀螺仪传感器数据和三轴加速度计传感器数据。位置曲线如图6所示,实线是导航解算系统解算的位置信息,虚线是GPS获得的实际位置信息。可以发现导航解算系统良好地跟踪了实际位置变化趋势,但是随着时间的推移,导航解算系统解算出的位置信息与实际位置信息偏差越来越大。

导航解算系统的误差引入主要因为基于MEMS的惯性传感器的误差较大,使用单一传感器进行姿态和位置解算会在姿态计算和速度计算环节两次引入积累误差。在实际使用中,载体使用的战术级高精度IMU,在一定的使用时间内,导航系统不会产生很大的积累误差。除此之外,发挥本系统动态特性好、更新速率快的优势,借助最优估计的方法,通过进行多种传感器的信息融合也可以收敛误差。

4 结论

针对现有小型无人机导航解算系统解算速度慢、多处理器臃肿可靠性差的缺点,文中提出了一种并行化的导航解算方法,并搭建了一种仅使用单一FPGA芯片为数据处理核心的小型高速导航解算系统,功能仿真验证了导航解算的高速性和准确性。车载实验验证了系统可以在实际中完成导航信息的解算工作。根据一次结算消耗时间可知系统理论拥有50 000 Hz的导航解算能力,在实际使用中,辅以足够精度的高速IMU,系统将会发挥小型化、高速率和低功耗的优势,在相关的小型无人机导航系统设计领域有重要借鉴意义。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)