基于FPGA的任意分频器设计

1、前言

分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如Altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。首先这种方法可以节省锁相环资源,再者这种方式只消耗不多的逻辑单元就可以达到对时钟的操作目的。

2、整数倍分频器的设计

2.1 偶数倍分频

偶数倍分频器的实现非常简单,只需要一个计数器进行计数就能实现。如需要N分频器(N为偶数),就可以由待分频的时钟触发计数器进行计数,当计数器从0计数到N/2-1时,将输出时钟进行翻转,并给计数器一个复位信号,以使下一个时钟开始从零计数。以此循环,就可以实现偶数倍分频。以10分频为例,相应的verilog代码如下:

regclk_div10;

reg [2:0]cnt;

always@(posedge clk or posedge rst) begin

if(rst)begin //复位

cnt<=0;

clk_div10<=0;

end

elseif(cnt==4) begin

cnt<=0; //清零

clk_div10<=~clk_div10; //时钟翻转

end

else

cnt<=cnt+1;

end

2.2 奇数倍分频

奇数倍分频因占空比不同,主要有以下两种方法。对于非50%占空比的分频,与偶数倍分频类似,只需要一个计数器就能实现特定占空比的时钟分频。如需要1/11占空比的十一分频时钟,可以在计数值为9和10时均进行时钟翻转,该方法也是产生抽样脉冲的有效方法。相应的verilog代码如下:

always @(posedge clk or posedge rst) begin

if(rst)begin //复位

cnt<=0;

clk_div11<=0;

end

elseif(cnt==9) begin

clk_div11<=~clk_div11; //时钟翻转

cnt<=cnt+1; //继续计数

end

elseif(cnt==10) begin

clk_div11<=~clk_div11; //时钟翻转

cnt<=0; //计数清零

end

else

cnt<=cnt+1;

end

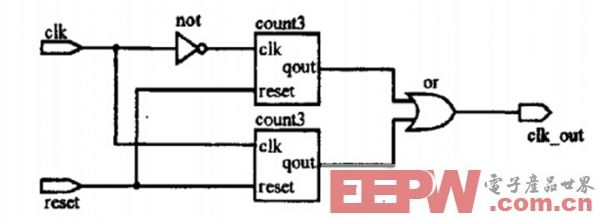

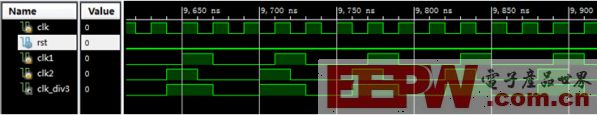

对于50%奇数分频器的设计,用到的思维是错位半个时钟并相或运算。具体实现步骤如下:分别利用待分频时钟的上升沿与下降沿进行((N-1)/2)/N分频,最后将这两个时钟进行或运算即可。以三分频为例,相应的电路原理图和时序仿真图如图1和图2所示,相应代码如下:

reg clk1;

reg[1:0]cnt1;

always@(posedge clk or posedge rst) begin

if(rst)begin //复位

cnt1<=0;

clk1<=0;

end

elseif(cnt1==1) begin

clk1<=~clk1; //时钟翻转

cnt1<=cnt1+1; //继续计数

end

elseif(cnt1==2) begin

clk1<=~clk1; //时钟翻转

cnt1<=0; //计数清零

end

else

cnt1<=cnt1+1;

end

reg clk2;

reg[1:0]cnt2;

always@(negedge clk or posedge rst) begin

if(rst)begin //复位

cnt2<=0;

clk2<=0;

end

elseif(cnt2==1) begin

clk2<=~clk2; //时钟翻转

cnt2<=cnt2+1; //继续计数

end

elseif(cnt2==2) begin

clk2<=~clk2; //时钟翻转

cnt2<=0; //计数清零

end

else

cnt2<=cnt2+1;

end

assignclk_div3=clk1 | clk2; //或运算

图1 50%占空比的三分频电路原理图

图2 50%占空比的三分频时序仿真图

3、小数倍分频器的设计

3.1 半整数分频器

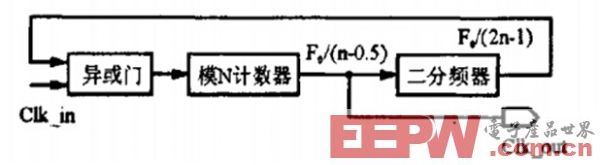

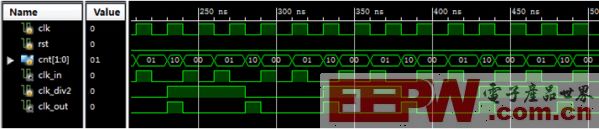

半整数N+0.5分频器设计思路:首先进行模N+1的计数,在计数到N时,将输出时钟赋值为1,而当回到计数0时,又赋值为0,这样,当计数值为N时,输出时钟才为1。因此,只要保持计数值N为半个时钟周期即是该设计的关键。从中可以发现。因为计数器是通过时钟上升沿计数,故可在计数为N时对计数触发时钟进行翻转,那么,时钟的下降沿就变成了上升沿。即在计数值为N期间的时钟下降沿变成了上升沿。也就是说,计数值N只保持了半个时钟周期。由于时钟翻转下降沿变成上升沿,因此,计数值变为0。所以,每产生一个N+0.5分频时钟的周期,触发时钟都要翻转一次。图3给出了通用半整数分频器的电路原理图。以2.5倍分频为例,相应的电路verilog代码如下,时序仿真图如图4所示。

//异或运算

assignclk_in=clk^clk_div2;

//模3计数器

reg clk_out;

reg [1:0]cnt;

always@(posedge clk_in or posedge rst) begin

if(rst)begin //复位

cnt<=0;

clk_out<=0;

end

elseif(cnt==1) begin

clk_out<=~clk_out; //时钟翻转

cnt<=cnt+1; //继续计数

end

elseif(cnt==2) begin

clk_out<=~clk_out; //时钟翻转

cnt<=0; //计数清零

end

else

cnt<=cnt+1;

end

//2分频

reg clk_div2;

always@(posedge clk_out or posedge rst) begin

if(rst) clk_div2<=0; //复位

else clk_div2=~clk_div2;

end

图3 通用半整数分频器的电路原理图

图4 2.5倍分频器

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)