基于FPGA的任意分频器设计

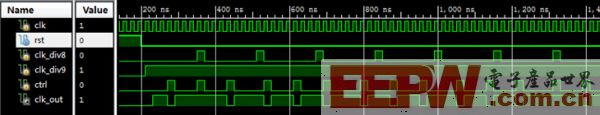

时序仿真图

3.2 任意小数分频器

小数分频器的实现方法有很多中,但其基本原理都一样的,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个计数周期的总体平均意义上获得一个小数分频比。一般而言,这种分频由于分频输出的时钟脉冲抖动很大,故在设计中的使用已经非常少。但是,这也是可以实现的。以8.7倍分频为例,本文仅仅给出双模前置小数分频原理的verilog代码及其仿真图(如图6),具体原理可以参考刘亚海的《基于FPGA的小数分频器的实现》以及毛为勇的《基于FPGA的任意小数分频器的设计》。

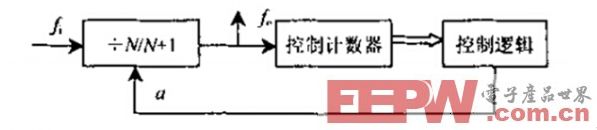

图5 小数分频器的电路原理图

//8分频

reg clk_div8;

reg[2:0]cnt_div8;

always@(posedge clk or posedge rst) begin

if(rst)begin //复位

clk_div8<=0;

cnt_div8<=0;

end

elseif(cnt_div8==3'd7) begin

clk_div8<=1; //置1

cnt_div8<=0;

end

elseif(cnt_div8==3'd0) begin

clk_div8<=0; //置0

cnt_div8<=cnt_div8+1;

end

else

cnt_div8<=cnt_div8+1;

end

//9分频

reg clk_div9;

reg[3:0]cnt_div9;

always@(posedge clk or posedge rst) begin

if(rst)begin //复位

clk_div9<=0;

cnt_div9<=0;

end

elseif(cnt_div9==3'd8) begin

clk_div9<=1; //置1

cnt_div9<=0;

end

elseif(cnt_div9==3'd0) begin

clk_div9<=0; //置0

cnt_div9<=cnt_div9+1;

end

else

cnt_div9<=cnt_div9+1;

end

//控制信号

parameterDiv8Num=3;

reg ctrl;

reg[3:0]AddValue;

always@(posedge clk or posedge rst) begin

if(rst)begin //复位

ctrl<=0;

AddValue<=10-7;

end

elseif(AddValue<10) begin

ctrl<=0;

AddValue<=AddValue+Div8Num;

end

else begin

ctrl<=1;

AddValue<=AddValue-10;

end

end

//选择输出

reg clk_out;

always @(ctrlor posedge clk or posedge rst) begin

if(rst) clk_out<=0; //复位

elseif(ctrl) clk_out<=clk_div8;

elseclk_out<=clk_div9;

end

图6 8.7分频器的时序仿真图

4、总结分频器是FPGA的基础,而且在FPGA逻辑电路设计的时候是经常使用的,希望大家对以上的整数倍分频和半整数倍分频能熟练掌握

。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)