基于FPGA的机载显示系统架构设计与优化

时间:11-05

来源:互联网

点击:

视频输出模块读数据,从DDR3中取出进行视频输出操作,取出的同时还能进行一些坐标变换操作,如平移、翻转、镜像等,读写数据量为

⑤ 预畸变参数读数据,用64位来存储每个像素点对应的四个预畸变参数,则读写数据量为

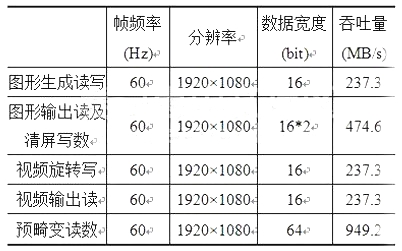

表 2为该系统数据吞吐量的计算表,其吞吐量合计为2135.7MB/s。DDR3的数据带宽为6400MB/s(800MHz*64bit),满足本文设计系统的数据吞吐量要求。

表2 优化后系统数据吞吐量计算表

结论

本文设计一种基于FPGA的机载显示系统架构,能够实现2D图形绘制,构成各种飞行参数画面,同时叠加外景视频图像。实时性方面,帧速率提升模块延迟最大为;BRAM资源占用方面,视频旋转算法需要279个36Kb的BRAM;DDR3吞吐量方面,系统吞吐量为2677.6 MB/s。

优化后的机载显示系统,实时性方面,帧速率提升模块延迟最大为;BRAM资源占用方面,视频旋转算法需要3个36Kb的BRAM;DDR3吞吐量方面,吞吐量为2135.7 MB/s。

经过对比分析,优化后的机载显示系统实时性提高、BRAM资源占用减少、吞吐量降低,整体性能得到了提升。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)