基于FPGA的机载显示系统架构设计与优化

随着航空电子技术的不断发展,现代机载视频图形显示系统对于实时性等性能的要求日益提高。常见的系统架构主要分为三种:

(1)基于GSP+VRAM+ASIC的架构,优点是图形ASIC能够有效提高图形显示质量和速度,缺点是国内复杂ASIC设计成本极高以及工艺还不成熟。

(2)基于DSP+FPGA的架构,优点是,充分发挥DSP对算法分析处理和FPGA对数据流并行执行的独特优势,提高图形处理的性能;缺点是,上层CPU端将OpenGL绘图函数封装后发给DSP,DSP拆分后再调用FPGA,系统的集成度不高,接口设计复杂。

(3)基于FPGA的SOPC架构,优点是,集成度非常高;缺点是逻辑与CPU整合到一起,不利于开发。

经过对比,机载视频图形显示系统的架构设计具有优化空间,值得进一步的深入研究,从而设计出实时性更高的方案。

本文设计一种基于FPGA的图形生成与视频处理系统,能够实现2D图形和字符的绘制,构成各种飞行参数画面,同时叠加外景视频图像。在保证显示质量的同时,对其进行优化,进一步提高实时性、减少内部BRAM的使用、降低DDR3的吞吐量。

1 总体架构设计

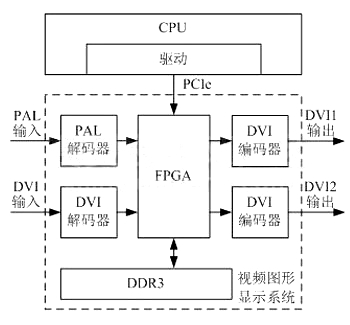

本系统总体设计方案如图 1所示。以Xilinx的Kintex-7 FPGA为核心,构建出一个实时性高的机载视频图形显示系统。上层CPU接收来自飞控、导航等系统的图形和视频控制命令,对数据进行格式化和预处理后,通过PCIe接口传送给FPGA。本文主要是进行FPGA内部逻辑模块的设计和优化。

图1 机载显示系统总体设计框图

2 机载显示系统架构设计

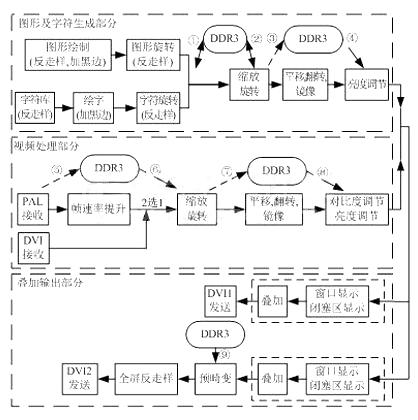

机载显示系统设计主要包括2D绘图、视频处理和叠加输出。2D绘图功能包括直线、圆、字符等的快速生成。视频处理功能包括输入视频选择、视频缩放、旋转、翻转等处理。叠加输出功能,将视频作为背景与图形叠加,送到两路DVI输出,一路经过预畸变校正后输出到平显上,另一路直接输出来进行地面记录。

为了满足上述功能,FPGA逻辑设计的整体流程图如图2所示。

图2 FPGA逻辑设计的整体流程图

2.1 实时性分析

视频处理既要实现单纯的外视频处理,同时能够实现叠加后视频处理。以旋转处理为例,若在单纯外视频旋转处理后,与图形叠加,再进行叠加后旋转处理,延迟非常大。因此为了提高实时性,考虑将图形整体和外视频分别进行旋转处理后,再相互叠加。整个流程中,帧速率提升模块延迟最大。

2.1.1 帧速率提升算法

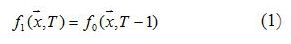

帧速率提升指在原有的图像帧之间插值出新的图像帧。常见的帧速率提升算法主要包括帧复制法、帧平均法和运动补偿法。综合考虑显示效果和实时性要求,最终选择帧复制法。帧复制法易于实现、计算量低。其表达式为:

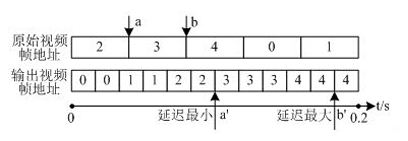

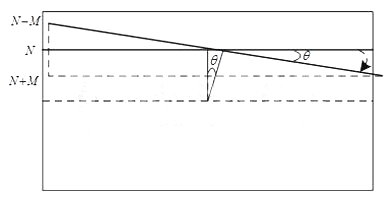

此处输入PAL视频帧速率为25帧/秒,输出DVI视频帧速率为60帧/秒,即在0.2s内将5帧图像插值到12帧。如图3所示,DDR3中开辟5帧存储空间用于存放25Hz的原始图像,在0.2 内输入5帧原始图像,输出12帧图像。延迟为PAL的1.5~2.6帧,最大延迟为。

图3 帧速率提升示意图

2.2 BRAM资源占用

本文设计的机载显示系统利用一片DDR3作为外部存储器,所有图形和视频数据都需要缓存到DDR3中。为了解决数据存储冲突,需要将数据先缓存到内部BRAM中。XC7k410T共有795个36Kb的BRAM。整个流程中,BRAM资源占用最大的是图形整体旋转和视频旋转模块。

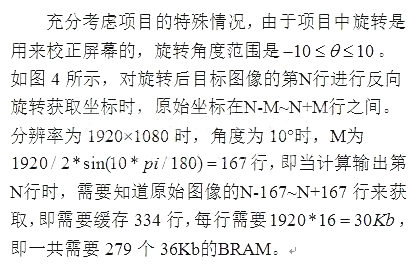

2.2.1 视频旋转算法

反向旋转映射优点是,旋转后坐标反向旋转,除了超出原始坐标范围的,在旋转前坐标中都能对应到浮点坐标,并可以用该坐标邻域的像素点来唯一确定该坐标的像素值,不会出现“空洞”现象。

图4 视频旋转算法示意图

2.3 DDR3吞吐量分析

本系统处理的数据量大,FPGA内部的存储资源无法满足数据存储要求,需要配置系统外部存储器DDR3。从图2可以看出,整个系统流程最多经过DDR3共9次,下面依次介绍每次读写DDR3的必要性和数据量。

① 图形及字符生成模块读写数据,由于图形及字符生成时,没有严格按照屏幕自上而下、自左而右的顺序,所以每一帧图形都需要存入到DDR3中,并等待一帧处理完再进行整体的其他处理。由于像素点操作会涉及到读取背景值,所以是双向的。考虑吞吐量最大的情况,即图形生成模块对每帧图形的一半像素点都进行一次读写操作,则图形生成模块读写数据量为

② 图形缩放模块读数据及清屏操作,由于缩放模块是对整个画面的处理,所以需要从DDR3中读取出来。而由于图形及字符不是对每个像素点都进行操作的,所以取出后,需要进行清屏操作。则读写数据量为474.6。

③ 图形旋转模块写数据,由于图形处理速度和视频处理速度不完全匹配,所以先将缩放及旋转后的数据存储到DDR3,等待视频处理完后,再统一取出

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)