基于FPGA的脉冲耦合神经网络的硬件实现

点是节约了FPGA资源的利用。改进模型的数学表达式与标准模型相似,只是馈送域不同。馈送域表达式为:

Fij[n]=Sij (2)

2.2 小数的定点表示方法

由于Vetilog无法直接定义小数类型,所以采用小数的定点表示法表示小数。考虑到灰度值为8位二进制数据,故小数的表示形式为8.8>,即整数位数和小数位数都为8位,整数的表示形式为8.0>,即整数位数为8位,小数位数为0位。由于并没有存储小数的位置信息,所以需要根据先前的约定对最后的结果进行截取。如式(3)所示,最后的运算结果为24位,低8位为小数部分,而利用Verilog的位操作运算截取中间8位即为更新后的灰度值。

8.8>*8.0>+8.8>*8.0>=16.8> (3)

2.3 PCNN参数选择

利用2.1节介绍的PCNN改进模型,描述单个神经元的PCNN算法。表1为本设计方案PCNN模型参数的经验设定,其阈值衰减设为每次运算后阈值的约0.9倍。为使算法利于硬件实现,实验中将设定神经元连接强度β=1,连接域增益VL=1。

其连接域邻域矩阵为:

2.4 系统整体设计框图

在进行图像处理时,需要把神经元与像素一一对应,神经网络的大小取决于图像的大小。如果需要处理的图像体积较大,那么硬件资源将被大量占用,继而需要更高规格的FPGA芯片来实现。本文介绍一个简单的PCNN硬件系统,可以处理3×3、8位的灰度图像。

PCNN在FPGA实现的系统框图如图2所示。系统分为5个主要的功能模块:时钟分频模块、串口接收模块、串并转换模块、PCNN模块和VGA显示模块。图中除PC机部分都在FPGA上实现。PC机包含上位机串口通信软件,常见的有VB串口通信助手、串口大师等,可实现串口的调试、测试、监控和过滤等功能。

系统需要完成的工作分为三大部分:图像的输入、图像的处理和图像的显示输出。系统详细的工作过程描述如下:PC机通过串口软件(如串口大师)发送图像数据,串口接收模块接收图像数据并通过模块内部的FIFO存储数据;串并转换模块将串口接收模块存储的图像数据并行输出给PCNN模块,等待处理;PCNN模块接收到图像数据后,开始进行迭代,并输出给VGA显示模块;VGA显示模块负责显示图像经PCNN模块处理后的二值序列,以观察PCNN的处理效果。由于本实验采用的FPGA实验平台提供的时钟频率为50 MHz,而串口接收模块、PCNN模块和VGA显示模块需要特定的时钟频率才能工作,所以必须设计时钟分频模块以产生满足要求的时钟频率。

3 系统仿真

由于考虑边缘神经元的特殊情况,设计了3种略有差异的神经元,即周围神经元输入分别为2、3和4的神经元。这里仅选取4输入的PCNN神经元进行仿真,神经元的阈值为200以验证神经元功能的正确性。通过选取了4个典型的图像灰度值S输入,分别为4、100、200和250,经仿真验证了单个神经元的正确性。

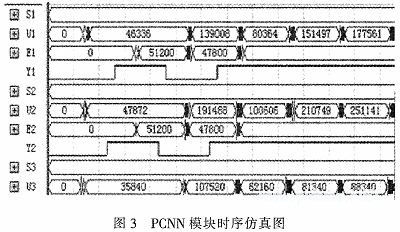

利用单个PCNN神经元,构建了包含9个PCNN神经元PCNN模块,能处理3×3大小的图像,通过网络迭代,得到理想的图像。通过串口输入数据:181、187、140、120、120、4、46、83、120,对PCNN模块进行了仿真。为了便于观察,选取其中3个神经元的时序仿真结果,如图3所示。由图3知,PCNN输出呈现0和1的不断变化,且能看出3个神经元中由于耦合效应产生了不同的结果。图3中S1~S3为9个像素灰度值的3个输入,Y1~Y3为图像经PCNN处理后3个二值序列值。

4 系统验证与分析

本实验以Altera Cyclone II开发平台为验证环境,选用Cyclone系列中的EP2C35F672芯片。利用串口软件发送网像数据,FPGA经PCNN处理后将二值结果显示在VGA显示器上。PCNN模块的时钟输入频率为100MHz,VGA显示模块的时钟输入频率为25 MHz。对于波特率,考虑到已经完成的串口接收模块,选取波特率115 200 bps,以匹配串口接收模块

的采样频率。数据位有8位,无检验位,包含1位停止位,传输数据以16进制的形式进行发送。

为了便于观察,考虑到显示器的刷新频率和人眼的视觉暂留,将PCNN网络的迭代处理频率设定为1 Hz,即显示器每1秒显示一次迭代效果图。图4为显示器前40次的显示效果。图中九宫格代表要处理的3×3输出图像,一个方格代表一个像素点。九宫格中灰色方框神经元点火,即输出为“1”。黑色方框代表神经元未点火,即输出为“0”。

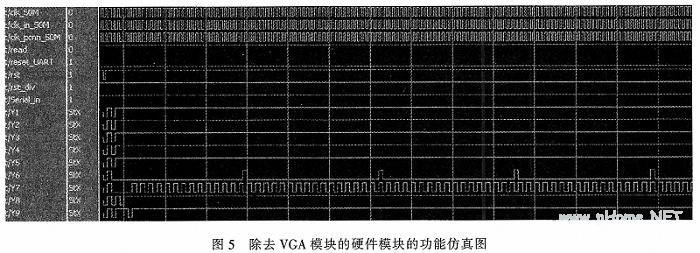

据实验平台的测试结果,与除去VGA模块的硬件模块ModelSim仿真结果进行了对比。图5为除去VGA模块的硬件模块的功能仿真图。图中高电平代表“1”,低电平代表“0”。

将图5与图4进行对比,图5中高电平代表图4中的黄色方块,图5中低电平代表图4中的黑色方块,两结果完全符合,这也验证了PCNN网络硬件实现的正确性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)