基于FPGA实现塔康地面信标信号发生器设计

时间:09-12

来源:互联网

点击:

周期性动作,系统完成一个周期的频率合成信号,累加器的溢出频率就是系统输出的信号频率。

本设计采用3级流水线设计,与普通相位累加器相比,虽然延时了两个时钟周期才输出结果,但是结果没有发生任何改变,反而大大提高了相位累加器的计算速率。

2.2.3 波形数据ROM模块

相位累加器的输出值即为波形数据ROM的查询地址,通过ROM进行相位-幅度的转换,就可以在给定的时间上确定波形的抽样幅值。ROM模块直接由QuartusII中MegaWizard Plug—in Manager工具产生。要产生ROM模块,需要.mif文件。可以利用Matlab产生.mif文件,但是其产生的.mif文件不可以直接使用,需要添加程序:

WIDTH=8;

DEPTH=64;

ADDRESS RADIX=UNS;

DATA_RADIX=UNS;

CONTENT BEGIN

……(省略号部分为数据)

END;

如果要更改数据参数,只需要对.mif文件进行更改,并对程序做相应的修改即可。

3 实验仿真

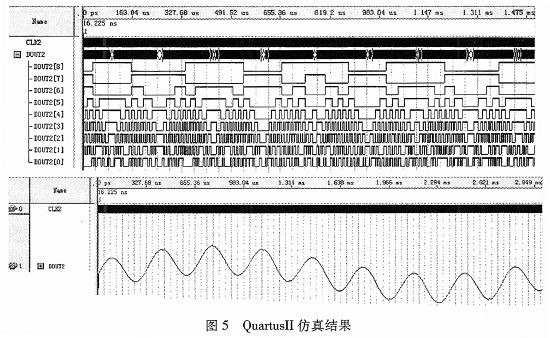

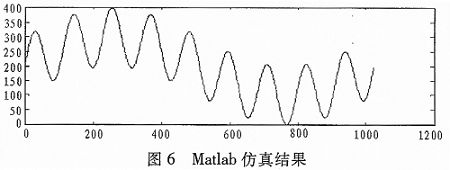

通过QuartusII建立Vector Waveform File文件来对软件系统进行仿真,结果如图5所示。用Matlab软件对仿真数据进行处理验证了软件部分设计的正确性,如图6所示。

4 结束语

该塔康地面信标信号发生器解决了某型飞机塔康设备检测仪方位信号的需求。在多次测试中,可以为其提供相应参数的发射信号。同时该发生器是基于DDS原理利用FPGA开发,大大缩减了设备开发时间,并且模块化设计为以后方案改进、软件优化、硬件更换提供方便,大大提高其灵活性。该塔康地面信标信号发生器已经交付相关部队,并取得良好效果。

- 基于Virtex 系列FPGA的可编程嵌入式信号处理背板的开发设计(06-06)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于现场总线的可重构数控系统的研究(12-20)

- 基于Verilog的多路相干DDS信号源设计(10-15)

- 基于FPGA的软件无线电高速数字信号处理(07-04)

- 基于DSP和FPGA的一种新型光伏并网控制方法(12-13)