基于FPGA实现塔康地面信标信号发生器设计

摘要:为满足某型飞机塔康设备检测仪器要求,对其提供稳定、可靠、多样的塔康地面信标信号。设计利用Altera公司的 EP4CE6E22C8为控制核心,以DAC813JP为DA转换器,运用DDS基本原理,通过QuartusII软件编写塔康地面信标信号发生器的每个单元模块,最终完成整个设计方案。并进行了Matlab与QuartusII相结合的仿真验证,同时设计连接了外部电路。相较于传统塔康地面信标信号发生器操作简单,便于升级,能够满足检测仪器的各项要求。

关键词:塔康信号;直接数字频率合成;现场可编程门阵列;数模转换器

塔康(TACAN)是战术空中导航系统的简称,是美国1955年研制并投入装备的近程无线电导航系统,是一种测角测距系统。“塔康”系统,又称作极坐标系统,能利用一个射频通道同时传递距离与方位信息,从而简化了机载设备,同时减少了对频段的占用。该系统可供飞机的出航、归航以及圆周飞行等航线飞行时使用,且在我军各类飞机上大量装备,因此设计塔康地面信标模拟器,用于检测机载塔康设备具有重要作用。由于FPGA具有快速、灵活控制、设计周期短,同时 DDS具有高分辨率,实现方法灵活的特点,所以本文研究了FPCA内嵌DDS技术实现塔康方位信号发生器的解决方案。

1 基本原理

1.1 塔康信号

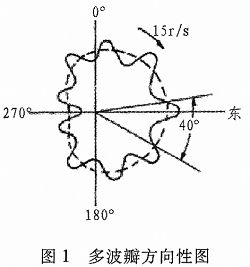

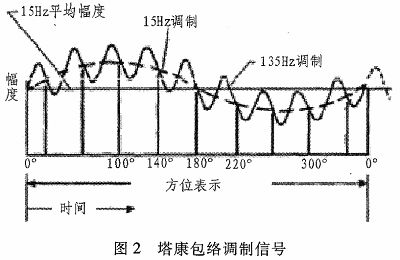

TACAN系统由塔康地面设备(塔康信标台)和机载设备两部分构成。该系统使用的是脉冲调制技术,并且它使用极坐标的方式来表示距离和方位。其中,系统通过天线的旋转产生一个旋转的多波瓣方向性图来获取方位,并且能够提供粗、精方位信息。如图1。塔康信号是由塔康地面信标台以15 Hz和135 Hz复合调制的旋转场向空中发射脉冲,形成15Hz和135 Hz脉冲包络调制信号,这些信号包括方位基准信号和方位包络信号,基准信号用脉冲编码来识别,包络信号则是利用脉冲序列幅度的方式来进行传送。其表达式为:

Q(t)=A0+A1sin(2πft)+A2sin(9×2πft) (1)

式中:f=15 Hz,A0为直流分量,A1、A2分别为大包络、小包络的调制幅度。经过调制后的信号就携带方位信息。在测量方位时,机载设备跟踪主、辅基准脉冲,计算出基准与包络相位零点之间的相位差,便可以完成定位工作。其调制信号如图2所示。

1.2 包络调制信号产生方案

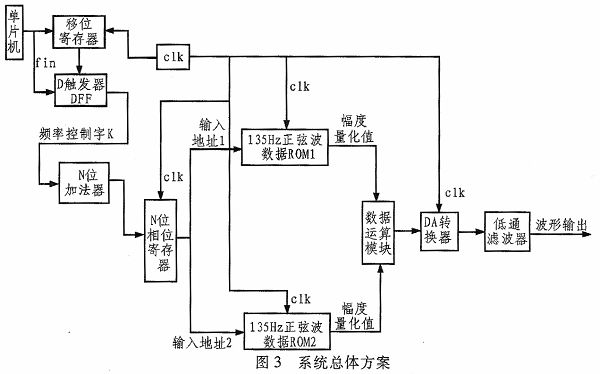

塔康信号外包络是由15 Hz和135 Hz正弦波叠加后形成的波形。因为该信号频率不高,本设计将输出的数字幅度值通过DAC芯片及调理电路转换为所需要的包络信号。本设计中信号通过在 FPGA内部应用DDS技术来产生,使用VHDL语言编写相位累加器、正弦波数据ROM,从而实现直接数字频率合成。最后将数字信号送到数模转换器 DAC,由DAC输出所需要的波形。塔康信号的AM调制包络是由15 Hz和135 Hz正弦波叠加而成。通过FPGA应用DDS技术,产生两路正弦波叠加后对应的幅度量化值,然后将波形数据送到数模转换器DAC 813JP转换为模拟波形,最后通过低通滤波器滤波送到调制电路使用。

2 系统方案设计

方案以Altera公司的Cyclone系列的EP1C12Q240C8芯片为核心,以QuartusII为软件平台,以FPGA开发板为硬件平台,在FPGA内部编写不同的功能模块,加上外扩的DA转换器和低通滤波器,完成塔康信号发生器的设计。其总体方案如图3所示。

2.1 系统外部电路设计

通过单片机为信号发生器提供信号所需要的参数以便满足检测仪不同的要求。数模转换器是数字电路和模拟电路连接的桥梁,FPGA输出的波形数据用DAC813JP进行D/A转换,然后输出信号经过I/V转换后,通过低通滤波器输出。本设计采用巴特沃兹二阶滤波器滤波。

外部电路的具体设计在此就不再赘述。

2.2 系统软件功能实现

本设计的实现软件功能的模块主要分为3个单元。首先用VHDL语言在软件平台QuartusII中编写每个单元并生成原理图,然后在顶层模块文件中将每个单元原理图连接起来,最后配置引脚并进行编译,从而完成整个软件部分的设计。

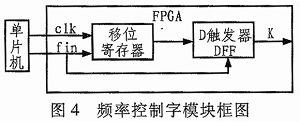

2.2.1 频率控制字模块

频率控制字K是二进制的相位增量值,它控制着最后输出波形频率的大小。作为相位累加器的输入,它的好坏直接影响整个系统的功能和性能。为产生所需要的频率控制字K,单片机输入的控制量通过串行外围设备接口与FPGA进行通信。其流程框图如图4所示。

2.2.2 相位累加器模块

相位累加器是FPGA逻辑控制的核心部分,一般由加法器和同步寄存器构成,实现相位累加。相位增量△φ=2π/2N对应的二进制表示为A△φ,即频率控制字K。K与输出频率f0呈简单的线性关系:

因此只要对相位的量化值进行累加,即可得到当前信号的向未知。在参考时钟的作用下,相位累加器进行线性的相位累加,当累加器溢出时即完成一个

- 基于Virtex 系列FPGA的可编程嵌入式信号处理背板的开发设计(06-06)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于现场总线的可重构数控系统的研究(12-20)

- 基于Verilog的多路相干DDS信号源设计(10-15)

- 基于FPGA的软件无线电高速数字信号处理(07-04)

- 基于DSP和FPGA的一种新型光伏并网控制方法(12-13)