基于KeyStone 器件建立鲁棒性系统

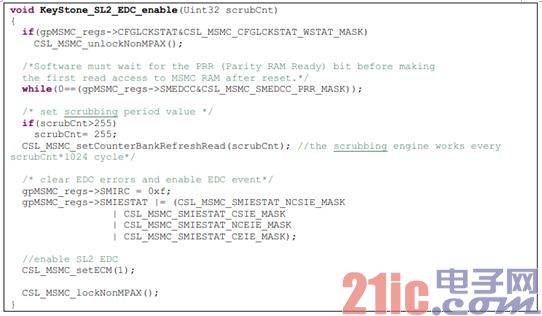

软件必须先检查SMEDCC 中的PRR 比特(校验RAM 是否准备好的状态信息)。

错误检测与纠正配置:DSP 复位后SL2 EDC 逻辑的刷新引擎被使能,并且会在后台产生校验信息。软件不需要像LL2 EDC 一样使用DMA 进行存储器刷新,只需要查询SMEDCC 寄存器中的PRR(校验RAM 准备)比特位来确认校验比特已经产生。为了使能错误纠正,SMEDCC 中的ECM比特同样应该使能。请注意,错误纠正逻辑会对从SL2 的读操作增加1 cycle 的时延(访问流水线增加了一级),不过访问吞吐量并不会降低。

下面是使能MSMC EDC 功能的例程:

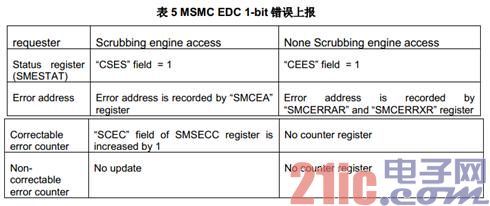

错误上报机制:MSMC 用户手册中有详细的错误上报机制信息,这里总结如下表。

请注意,由刷新引擎上报的错误地址是从0 开始的地址偏移,而为非刷新访问记录的错误地址是器件中从0x0C000000 开始的SL2 地址。

MSMC EDC 功能验证:可以通过设置SMEDCTST 寄存器中的PFn 比特位(bit0~3)来暂停MSMC EDC 逻辑。SMEDCTST 的地址偏移是0x58。每个SL2 RAM bank 对应PFn 中一个比特(PF0~3 与bank0~3 依次对应),每个比特可以用于禁止对校验RAM 的写操作。这样可以冻结bank 对应的校验RAM,因此可以通过故意注入错误来破坏SL2 存储内容与校验信息的一致性,从而测试检测纠正逻辑。具体的顺序如下:

1. 向测试bank 中的某一个位置写一个已知值,这样可以正确地为这个位置初始化一个校验值。

2. 向SMEDCSTST 对应的PF 比特写1 以冻结该校验值。

3. 向上述被写的位置写任意字节来改变该位置的数值,如果检验纠正功能则写一个1-bit 差异的值,如果检验检测功能则写一个存在2-bit 差异的值。此时该位置的校验值与其存储的数值没有同步。

4. 读回该位置的值,将会产生所选类型的校验错误。

与本文对应的例程中提供了相应的代码用于验证SL2 EDC 功能,对应的函数为SL2_EDC_test()。

4 其它鲁棒性特性

4.1 看门狗定时器

对应看门狗定时器的基本知识,请参考“KeyStone Architecture Timer64 User Guide(SPRUGV5)”中“看门狗定时器模式”章节。

定时器0~(N-1)可用于N 个core 的看门狗。在TCI6614 中定时器8 是ARM 的看门狗定时器。

在看门狗模式下,定时器倒计时到0 时产生一个事件。需要由软件在倒计时终止前向定时器写数,然后计数重新开始。如果计数到0,会产生一个定时器事件。看门狗定时器事件可以触发本核复位、器件复位或者NMI 异常,这可以通过配置相应器件手册中描述的“复位复用寄存器(RSTMUXx)”来选择。

使看门狗事件触发NMI 异常具有更高的灵活性,在NMI 异常服务函数中,错误的原因及某些关键的状态信息可以被记录下来,或者上报给上位机来进行故障分析,然后如果它不能自恢复则可以再由软件来复位器件。

4.2 EDMA 错误检测

关于基本的EDMA CC 错误信息可以参考“KeyStone Architecture Enhanced Direct Memory Access(EDMA3)Controller User Guide(SPRUGS5)”中的“错误中断”章节。

关于基本的EDMA TC 错误信息可以参考“KeyStone Architecture Enhanced Direct Memory Access(EDMA3) Controller User Guide(SPRUGS5)”中的“错误产生”章节。

所有的EDMA 错误事件可作为异常被路由到 CorePac。

事件丢失错误是一种最常见的EDMA CC 错误,意味着EDMA 不能按要求及时完成数据的传输,或者错误的事件触发了不应该的EDMA 传输。

总线错误是一种最常见的EDMA TC 错误,通常意味着EDMA 访问了错误的地址(如预留地址或受保护的地址)。

4.3 中断丢失检测

中断丢失或遗漏是实时系统中常见也是常被忽略的问题。中断丢失检测是一种用于捕捉这种异常的有效方法。对基本的中断丢失检测信息参考“TMS320C66x DSP CorePac User Guide(SPRUGW0)”中“中断错误事件”章节。

软件系统应该对路由到DSP core 且有对应软件服务的中断使能中断丢失检测。在所有中断配置完毕后可以添加如下代码使能中断丢失检测:

![]()

注意,当使能中断丢失检测并在CCS/Emulator 下使用断点或单步进行调测时,由于在仿真停止时中断没有被响应,所有此时中断丢失错误上报的概率很高。如果想忽略它,可以在调测时暂时对某些或全部中断关闭中断丢失检测,但是注意不要忘记在正式发布的程序中重新使能该功能。

5 异常处理

关于异常处理的基本信息参考“TMS320C66x DSP CPU and Instruction Set Reference Guide(SPRUGH7)”中“CPU 异常”一节。

关于中断或异常事件路由的基本信息参考“TMS320C66x DSP CorePac User Gui

- HyperLink编程和性能考量(01-15)

- 在KeyStone 器件实现IEEE1588 时钟方案(10-15)

- 基于多核处理器的弹载嵌入式系统设计研究(02-18)

- Navigator Runtime 最大限度提高多内核效率(05-08)

- 基于KeyStone DSP的多核视频处理技术(09-15)

- KeyStone多核SoC工具套件: 单个平台满足所有需求(09-07)