基于KeyStone 器件建立鲁棒性系统

x0000_0000~0x07FF_FFFF 进行访问时,在C66x CorePac 内部进行地址解析。这块地址范围包括内部及外部配置总线,及L1D、L1P、L2 存储空间。

对位于0x0C00_0000~0x0FFF_FFFF 区间的逻辑地址访问时,会经过L1 cache,并且在读操作时会经过预取缓存,与该地址范围对应的内存属性配置寄存器MAR 是硬件拉死的,不可修改。也就是说对该逻辑地址空间的访问在进入XMC MPAX 之前不会经过L2 cache,所以这块逻辑地址空间称为“快速SL2 RAM 路径”。

对大于等于0x1000_0000 的逻辑地址访问会首先经过L2 cache 控制器,然后经过XMC MPAX,这种常规路径会增加一个cycle 的时延。

根据上述配置例子,在访问SL2 时,采用逻辑地址0x0C00_0000 的访问速率高于使用重映射后的逻辑地址0x1800_0000。但是0x1800_0000 对应的内存属性寄存器MAR 是可编程的,因此可以配置通过0x1800_0000 访问的SL2 为non-cacheable 及non-prefetchable。

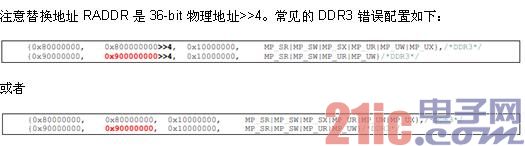

注意DDR3 起始物理地址为0x8:0000_0000,而0x9:0000_0000 相对起始地址有4GB 的偏移,在大多数系统中这是一个非法的地址。

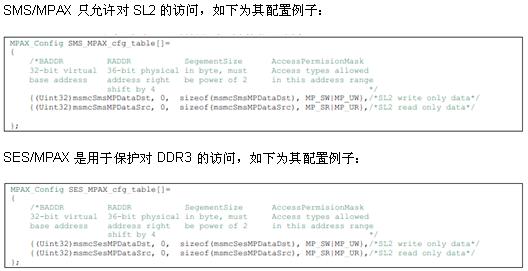

在真实系统中,应该充分利用好MPAX 的所有片段更好地将存储空间划分成尽可能多的小片,并仔细设定各个分片的访问限定属性。

不用的地址不应该映射,MPAX 会拒绝对未映射的地址访问并上报异常事件,从而有助于捕获软件错误。

当两个master 通过共享memory 交换数据时,应该确保两个master 使用的逻辑地址映射到相同的物理地址。

注意EDMA 的权限ID 是继承于对其配置的CorePac。

警告:

在修改一条 MPAX 表项时,需要确保此时没有对该表项所覆盖地址的访问。在修改之前,需要先将该表项覆盖地址对应的cache 及预取缓存中的数据进行回写及失效操作。

对于MPAX 的配置,推荐在程序开始之初且没有使用任何共享存储空间之前完成。用于CorePac MPAX 配置的代码和数据应该放在LL2。

如果要运行时动态修改一个MPAX 表项,安全的方法是先将新的配置写到一个未使用的编号高度表项,然后清掉旧的表项。这是由于编号高度表项的优先级高于编号低端表项。

在修改MPAX 表项之前需要先执行如下操作:

1. 将MPAX 表项对应的存储空间内容从cache 中剔除出去。即使对于属性为不可写的存储空间,应该使用CACHE_wbInvL2()而非CACHE_inv L2()。

2. 如果对受影响的存储器空间使能了预取功能,则需要对预取缓存执行失效操作。

3. 执行“MFENCE”确保回写及失效操作完成。

CorePac 的MPAX 寄存器受CorePac 的内存保护寄存器锁保护。SES 及SMS 的MPAX 内存保护属性寄存器被MSMC 内部分别用于SES 及SMS 的锁保护。MSMC 内部其他寄存器被MSMC内部用于非MPAX 的锁保护。

2.3 外设配置端口保护 – MPU

关于MPU 的基本信息参考“KeyStone Architecture Memory Protection Unit User Guide (SPRUGW5)”。

MPU0、MPU1、MPU2 及MPU3 对所有KeyStone 1 器件是相同的。但是对于不同的器件,其附加MPU 的个数,每个MPU 支持的地址范围表项数,MPU 的默认配置均有所差异。具体可参考相关器件手册的“内存保护单元(MPU)”章节。

MPU 与MPAX 的区别在于,如果访问地址不在MPU 任何一个地址范围内,则该地址访问是允许的;而当该地址与MPAX 中任意表项地址范围不匹配时,则该地址访问被拒绝。

注意,如果没有被MPPA 的设置所拒绝,MPU 单元默认所有的访问都是许可的。对于一个地址访问,MPU 首先将访问的权限ID 与MPPA 寄存器的AID bit 配置进行核对,如果与权限ID 对应的AID bit 为0,则不需要核对地址范围,该访问被许可。如MPPA=0 则允许所有的对该空间的访问,如果要拒绝任意对该空间的访问则需要将MPPA 配置为0x03FFFC00。L1 及LL2 内存保护的MPPA 设置则有所不同,当MPPA 中AID bit 为0 是拒绝相应的访问。

当传输与MPU 中多个地址范围匹配时,所有重叠的范围必须允许其访问,否则该访问会被拒绝。最终赋予的访问权限与所有匹配表项中最低的权限等级一致。如某传输与2 个表项匹配,其中一个是RW,另一个是RX,则最终的权限是R。这与MPAX 也是不一样的。如果一个地址落入多个MPAX 表项,编号高的表项优先于编号低的表项。MPAX 只会用编号最高的表项决定权限,并忽略其他匹配的表项。

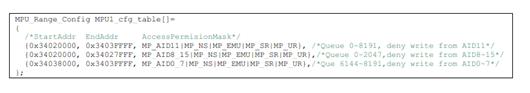

如下与本文对应例程中一个对MPU1 的配置例子。每行代表MPU 中一个配置范围。

如上配置知,队列保护如下:

· 队列0~2047 只可由AID0~7 进行写(PUSH)操作;

· 队列2048~6143 可由AID11 以外所有的AID 进行写(PUSH)操作;

· 队列6144~8191 只

- HyperLink编程和性能考量(01-15)

- 在KeyStone 器件实现IEEE1588 时钟方案(10-15)

- 基于多核处理器的弹载嵌入式系统设计研究(02-18)

- Navigator Runtime 最大限度提高多内核效率(05-08)

- 基于KeyStone DSP的多核视频处理技术(09-15)

- KeyStone多核SoC工具套件: 单个平台满足所有需求(09-07)