MSP430F5529 (七)定时器B

器(比较模式下)

TA里面,我们在TACCRn中写入要比较的数值,然后让TAR中的计数值和TACCRn比较,如果相等了,相应的标志位就会置位;

TB里面,不仅有TB0CCRn,还多了一个二级缓存器TB0CLn。TB0CLn不能被直接进行操作,它的值只能来源于TB0CCRn。计数的时候,TB0R中的计数值不和TB0CCRn比较,而是和TB0CLn进行比较。

二级缓冲是为了防止我们在修改TB0CCRn的值的时候,对计数产生影响。因为计数器不直接和TB0CCRn比较,而是TB0CCRn把值赋给TB0CLn,由TB0CLn去和TB0R进行比较。所以也就有了CLLD位控制比较寄存器缓冲装载模式:(当向TB0CCRn中重新写数时)

00TB0CCRn的值立即装载到TB0CLn

01当TB0R的值计到0时,进行装载

10增模式或者连续模式下,TBR0值计到0时,进行装载;

增减模式下,TBR0计数到TBCL0时,开始装载;

11 TBR0计数到TBCL0时,开始装载;

7.3.4比较器可以被分组

TA没有二级缓冲寄存器,而且本来的TACCRn也只能被单 独使用。

对于TB:

TBCLGGRP:TB0CLn二级缓冲寄存器分组控制

00:每个TB0CLn独立使用

01:TB0CL1+TB0CL2作为一组(TB0CCR1的CLLD位控制整组数据更新)

TB0CL3+TB0CL4作为一组(TB0CCR3的CLLD位控制整组数据更新)

TB0CL5+TB0CL6作为一组(TB0CCR5的CLLD位控制整组数据更新)

10:TB0CL1、2、3一组,(TB0CCR1的CLLD位控制整组数据更新)

TB0CL4、5、6一组,(TB0CCR4的CLLD位控制整组数据更新)

11:TB0CL0、1、2、3、4、5、6整合为一组,

(TB0CCR1的CLLD位控制整组数据更新)

所谓的分组,就是该组的数据要同时更新。

以10模式下的TB0CL1、2、3这组为例:

TB0CCTL1中的CLLD设置为01,即TB0R计数到0时,TB0CCR1就会把值装载(更新)到TB0CL2中,同时TB0CCR2就会把值装载(更新)到TB0CL2中,同时TB0CCR3也会把值装载(更新)到TB0CL3中。无论TB0CCRn中的值有几个发生了变化,但它们都只会同时更新TB0CLn。

一个重要的应用:

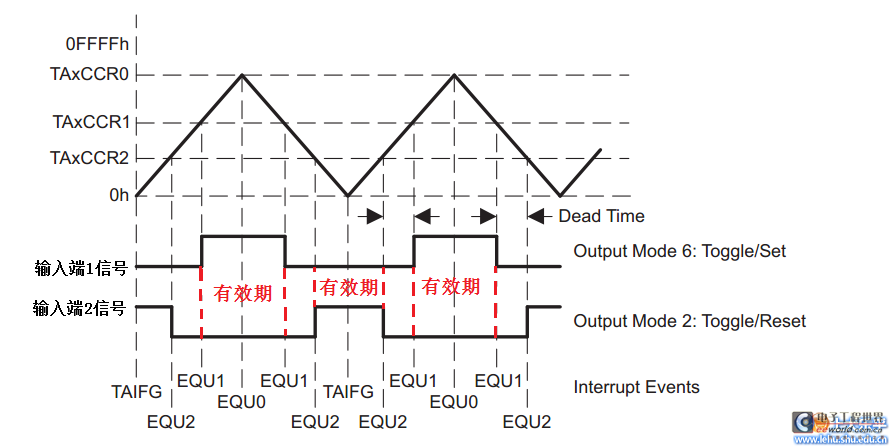

如图,增减模式下,可以用来产生有死区时间(dead time)的信号。

我们知道有一种H桥电路结构,该电路有一般有两个输入端,而且这两个输入端(1和2)严禁同时输入高电平。那么该怎么产生驱动该电路的信号呢:

但是,如果我们想要在系统运行的时候,修改死区时间怎么办。那只有修改

比较器里面的数值了。这样就有问题了,如果两个比较器数值没有同时修改,那么就有可能产生同时为高电平的情况,这就很危险了。所以,我们把比较器分组,这样数据同时更新,就不会有这样的担心了。

MSP430F5529定时器 相关文章:

- MSP430F5529 (六)定时器Timer_A-1(11-28)

- MSP430F5529 (六)定时器Timer_A-2(11-28)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)