基于FPGA和多DSP的多总线并行处理器设计

引言

随着国防工业对精确制导武器要求的不断提高,武器系统总体设计方案的日趋复杂,以及电子元器件水平的飞速发展。导引头信号处理器的功能越来越复杂,硬件规模越来越大,处理速度也越来越高,而且产品的更新速度加快,生命周期缩短。实现功能强、性能指标高、抗干扰能力强、工作稳定可靠、体积小、功耗低、结构紧凑合理符合弹载要求的导引头信号处理器已经势在必行。过去单一采用单片机或DSP处理器搭建信号处理器已经不能满足要求。针对现有技术的不足之处,本文提出一种基于FPGA和3片DSP的目标识别与定位并行处理器。主要解决现在信号处理方法在水中兵器中的应用难题,提高兵器的智能化与战技指标。

1 系统设计方案

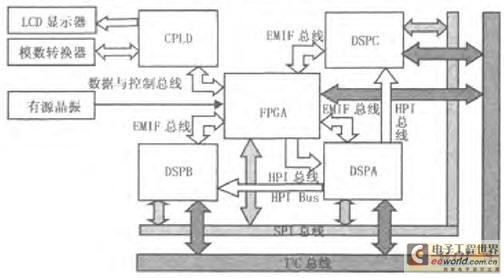

本文设计了一种基于FPGA和3片DSP的目标识别与定位并行处理器。如图1所示,其特征在于:

(1)端口控制CPLD芯片、系统数据缓存与通信FPGA芯片、3个DSP处理芯片、系统电源模块、多路并行ADC模数转换芯片、有源晶体振荡器、LCD输出显示模块。

(2)将FPGA作为系统数据缓存、通信与控制中枢,以此为核心,通过数据与控制总线联接端口控制CPLD芯片,通过EMIF总线分别联接DSP(A)、DSP (B)和DS (C)处理芯片。

(3)端口控制CPLD芯片的输入端联接多路并行ADC模数转换芯片,输出端口联接LCD输出显示模块。

(4)有源晶体振荡器与FPGA芯片联接,FPGA芯片将有源晶体振荡器分为4路时钟信号输出,分别输出到CPLD和3片DSP芯片。

(5)系统电源模块为5V单电源供电,产生系统需要的3. 3V、2.5V、1.2V电源电压。

(6)多路并行ADC模数转换芯片对阵列接收信号进行采集,将采集的数据传输到CPLD缓存空间中,CPLD缓存空间半满后将数据传输到FPGA数据存储FIFO中,并将数据转换为复数数据保存;

(7) DSP (A)、DSP (B)和DSP (C)处理芯片对于采集的数据采用并行分离算法进行盲分离和盲解卷积定位,然后对盲分离各信号进行支持向量机分类,DSP (A)、DSP (B)和DSP (C)处理芯片分别并行对待识别分离信号进行3类舰船的信号的识别,比较3个DSP的识别结果,完成目标信号分类,将分离信号识别完毕,输出至FPGA综合定位与分类结毕,并将结果通过CPLD输出到LCD显示。

图1系统原理图

多通道ADC对阵列接收信号进行采集,将采集数据传输到CPLD缓存空间中,CPLD缓存空间半满后将散据传输到FPGA数据存储FIFO中,井将数据转换为复数数据保存,等待处理,从而实现了ADC的连续高速采集,一批数据采集完成后,用3DSP盲信号并行分离算法进行盲分离和盲解卷积定位,之后.对盲分离各信号进行支持向量机分类,3片DSP分别并行对待识别分离信号进行3类舰船的信号的识别,比较3个DSP的识别结果,完成目标信号分类,直到讲待分类的分离信号识别完毕,最后由FPGA综合定位与分类结果,并将结果通过CPLD输出到LCD显示。

2 具体系统设计

FPGA在实时并行计算实现标准数字信号处理算法的能力远强于DSP,因此数字接收系统信号处理要用到的FIR滤渡、FFT、IFFT等算法,在FPGA中实现要远快于DSP,且FPGA厂商提供了非常丰富易用的能实现数字信号处理的参数Core,可以大大简化开发过程。而且,FPGA有大量乘法器和存储器资源,支持设计高度并行的架构,可有效提高实时性、集成度和稳定性。而DSP用来进行其他复杂信号处理,比如自动目标识别、抗干扰等。

2.1电路构成

本系统包括一片端口控制CPLD芯片,一片系统数据缓存与通信FPGA芯片,三片DSP处理芯片,一片串口通信芯片,一片USB通信芯片,一片3.3V电源芯片,一片2.5V电源芯片,一片1. 2V电源芯片,一片多路并行ADC模数转换芯片.一片多路并行DAC数模转换芯片,一片Flash存储器,三片SRAM存储器,一片EPCS存储器,一个有源晶体振荡器.一个无源晶体振荡器,一个PS2键盘接口,一个USB接口,一个申口接口,一个SD卡卡座,一个LCD显示模块.

DSP芯片:TMS320C6713 DSP是TI推出的一款C6000系列32位高速浮点型DSP芯片,时钟最高频率为225MHz,最大处理能力达到2400MIPS,采用二级缓冲处理,4kByte直接匹配的程序缓冲LIP.4kByte可匹配的数据缓冲LID,256kByteL2额外匹配内存。32位外部存储器接口,可无缝连接SRAM,EPROM、Flash、SBSRAM和SDRAM;其外设EDMA支持无需CPU参与可以在允许的地址空间里传送数据,扩展总线,具有主机口和I/O端口操作等功能,多通道缓冲串口,其通过配置能和多种串行通信接口通信。两个32位通用定时器等。

FPGA芯片:EP3C25Q240C8N是ALTERA推出的一款功耗最低、成奉最低的Cyclone III系列高性能FPGA,具有24,624个逻辑单元,66个M9K存储块,总共608,256

FPGADSP多总线并行处 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)