基于FPGA和多DSP的多总线并行处理器设计

Bits的RAM,66十18 *18乘法器,4个PLL,另外,其内部还有20个可独立工作的时钟网络,240个外部引脚提供了148个通用I/O,可以完全满足多DSP的互联。其丰富的内部资源可以提供多种数据交换模式,进一步采用嵌入式Nios II处理器,其本身亦可以作为强大的数据处理器使用,配个其并行的计算结构和较高的运行频宰,特别适合效据先期处理的计算处理器使用。

CPLD芯片:EPM3128ATI100 -10N是ALTERA推出的一款基于CMOS EEPROM结构的MAX 3000A系列的高性能可编程器件,具有2,500可用逻辑门,128个宏单元,多大98个可用I/O口,最高时钟频率192. 3MHz,接口电压兼容Sv.3.3V,2.SV等,是理想的数据转换与通信控制器件,系统中用于扩充FPGA的I/O口,作为数据转换、缓冲与通信桥路。

2.2基于FPGA的多DSP系统接口电路设计

在本系统中,要求利用一个主处理器来控制3片DSP,完成主处理器与各DSP的控制及散据传输,为了提高传输速率,保证控制的灵活性、准确性,我们利用FPGA设计一种综合实用的多DSP的接口电路。

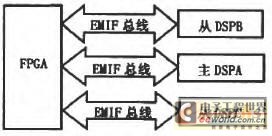

由于系统中包含3片DSP,设计时采用系统层次化,结构模块化、数据传输高速化的设计思想,利用FPGA作为接口设计的部件,实现系统的接口电路原理如图2所示。

图2 FPGA与DSP通信框图

系统层次化体现在控制结构之中,考虑到多片DSP的接口t控制与数据传输以层次化结构为主,以寄存器作为控制接口的物理层,每个DSP均有其自身的控制寄存器,以实现多个DSP的控制,以FIFO作为数据传输的物理层。在软件设计中增加了控制的灵活性及数据传输的高速率。结构模块化体现在DSP组的结构中,根据多块DSP接口的特点,在系统结构设计中,将3片DSP用一十FPGA来完成物理层硬件接口电路,这样使得系统结构清晰,模块扩充灵活方便,又可节省费用。

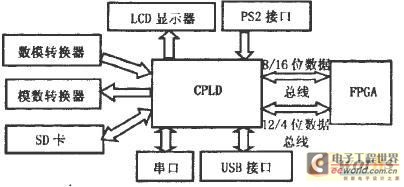

2.3系统外部接口设计

根据数据处理需求,系统设计了丰富的外围接口电路,并通过FPGA扩展的CPLD来进行管理。如图3所示.

图3 系统功能框图

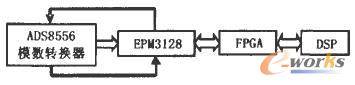

2.4 ADC设计

图4为系统设计的.NDC硬件框图.基于CPLD、FPGA和DSP的多通道同步数据采集系统主要由数据采集模块、数据处理模块以及散据接口模块3部分构成。前端由传感器输入的模拟信号经信号调理模块的整形放大后,输入到A/D转换模块中,模拟量转变为数字量,可编程逻辑器件(CPLD)控制A/D转换器,按照设定的采样率采集数据,将采集到的数据通过总线写入FIFO,FIFO半满时,发送一次半满信号,FPGA接收到中断后立即将一帧数据从FIFO中读入到数据处理模块,进行初步处理并通知相应的DSP对其进行调用,做进一步分析。

图4 ADC硬件框图

该系统的A/D转换模块选用TI公司的ADS8556型A/D转换器,该件支持6通道信号差分输入,有3组信号采集控制端,每组控制2路信号.16位精度,每通道的转换速度高达450 kHz。支持高速并行数据输出接口,数据输出接口包括直接地址选择模式、CYCLE模式、FIFO模式。

2.5 CPLD部分设计

CPLD控制部分:CPLD1控制ADS8556包括控制A/D转换器的采样率以及数据量化输出模式等,同时控制CS信号可有效抑制噪声;系统时钟输入为50 MHz,CPLD对其分频产生20MHz时钟以触发A/D转换器,同时产生200kH的采样信号。

2.6数据帧格式设计

CPLD将A/D转换后的数据不断写入FIFO,当2048字节数据写入FIFO后,CPLD添加16位的帧标志及16位的帧计数,即数据格式为:被采集数据+帧标志+帧计数。

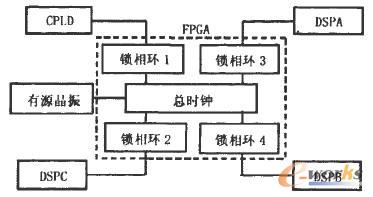

2.7系统时钟设计

对于多DSP并行处理系统而言,系统各部分的时钟配合以同步十分关键,不仅关系到系统的稳定运行,更重要的是系统内部的信息交换严重依赖于可靠地时钟同步,特别是采用同步FIFO或RAM来传递数据的场合,同时可靠统一的系统时钟也有利于数据传输效率的提升。

考虑到本系统容纳了5片核心的处理单元,各系统如果分别采用各自的时钟源,很难确保时钟的统一与同步性,为信息的同步交换效率埋下了隐患,而且从工程中来看,不光增大了系统的设计分复杂度,扩大了电路布板面积,而且引入了多处的干扰源,为此,系统从总体设计上,依据FPGA丰富灵活的内部时钟资源,提出采用如图5所示方法,将FPGA各分时钟作为其他给分系统的时钟源,从而简化了电路设计,提高了时钟的一致性与可靠性。

2.8系统总线设计

为了充分发挥系统多CPU工作性能,系统除了基于FPGA的EMIF总线外,还冗余设计了HPI,SPI和I2C总线,用于DSP之间的信息传递,控制与程序加载等。如图所示多总线结构如图1。

图5 系统时钟设计图

2.8.1 HPI主机接口

系统HPI (hardware platform interface)是一个16 b宽度的对外接口,主要用于主处理器DSP通过HPI向附

FPGADSP多总线并行处 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)