强大的防盗定位追踪系统方案,硬件原理、结构框图、软件流程、源码打包奉送

roBlaze_0

MicroBlaze_0是基于Spartan-3E的微处理器IP核, MicroBlaze_0处理器采用RISC架构和哈佛结构的32位指令和数据总线。在本系统中,MicroBlaze是本系统中运算与控制的核心,它可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据。为了提高性能,MicroBlaze中设指令缓存和数据缓存。

MicroBlaze通过LMB与BRAM相连,通过dlmb对BRAM进行数据的读写,通过ilmb从BRAM中读取指令。MicroBlaze_0通过OPB来访问低速和低性能的系统资源,如LED,16M×8Flash,RS23_DTE,LCD等。下面再对这LMB和OPB两种总线加以介绍。

LMB

LMB(Local Memory Bus,局部存储总线,如图中dlmb与ilmb)是MicroBlaze与BRAM之间的信息传送线,分为dlmb(数据局部存储总线)和ilmb(指令局部存储总线),两种总线宽度均为32位。dlmb用于MicroBlaze从BRAM中读写数据,ilmb传送MicroBlaze从BRAM中读取的指令。

OPB

OPB(On-chip Peripheral Bus,片上外设总线)提供了MicroBlaze与低速外接设备之间的数据通路。OPB是一种完全同步总线, 它的功能处于一个单独的总线层级。它不是直接连接到处理器内核的。OPB接口提供分离的32 位地址总线和32位数据总线。处理器内核可以借助“PLB to OPB”桥,通过OPB访问从外设。作为OPB总线控制器的外设可以借助“OPB to PLB”桥,通过PLB访问存储器。

OPB上挂接了各种类型的外设。在本系统中,OPB上挂接的外设有Spartan-3E开发板上的Buttons_4Bit,DDR_SDRAM_16Mx16,DIP_Switches_4Bit,Flash_16Mx8,LEDs_8Bit,RS232_DTE,RS232_DCE,LCD,OPB_Timer。

BRAM

BRAM(Block Random Access Memory,块随机存储器)用于存放MicroBlaze核要运行的程序指令以及需要处理的数据或中间结果等。

BRAM通过LMB接口与LMB相连,进而与处理器相连。ilmb_cntlr为指令局部存储总线控制器,BRAM通过PORTA与ilmb_cntlr相连,ilmb_cntlr负责控制指令数据在LMB总线上的传送;dlmb_cntlr为数据局部存储总线控制器,BRAM通过PORTB与dlmb_cntlr相连,dlmb_cntlr负责控制数据在LMB总线上的传送。

Buttons_4Bit

Spartan-3E开发板上的4个瞬时按钮开关BTN_NORTH、BTN_EAST、BTN_SOUTH和 BTN_WEST及1个Rotary Push-Button Switch(旋转按钮)中使用了BTN_SOUTH和旋转按钮用于用户输入。其中BTN_SOUTH为复位键以重新执行程序,旋转按钮用于接收用户的追踪定位请求。其对应的引脚约束如下:

Net fpga_0_Buttons_4Bit_GPIO_in_pin0> LOC=D18 | PULLDOWN;

Net fpga_0_Buttons_4Bit_GPIO_in_pin1> LOC=H13 | PULLDOWN;

Net fpga_0_Buttons_4Bit_GPIO_in_pin2> LOC=V4 | PULLDOWN;

Net fpga_0_Buttons_4Bit_GPIO_in_pin3> LOC=V16 | PULLDOWN;

Flash_16Mx8

本系统采用了Intel Strata Flash Parallel NOR Flash PROM来存放需要运行的程序。由于需要FPGA启动后自动加载程序并运行程序,所以需要把程序存储在非易失性存储器中。在本系统中选用16Mx8bit Flash存放程序(.elf文件)。FPGA启动时,存放在Flash中的FPGA配置信息与应用软件程序通过OPB总线自动加载到FPGA运行。其引脚约束较为复杂,在此只列出其控制引脚的约束语句:

Net fpga_0_FLASH_16Mx8_Mem_OEN_pin LOC=c18;

Net fpga_0_FLASH_16Mx8_Mem_OEN_pin IOSTANDARD = LVCMOS33;

Net fpga_0_FLASH_16Mx8_Mem_WEN_pin LOC=d17;

Net fpga_0_FLASH_16Mx8_Mem_WEN_pin IOSTANDARD = LVCMOS33;

Net fpga_0_FLASH_16Mx8_Mem_CEN_pin0> LOC=d16;

Net fpga_0_FLASH_16Mx8_Mem_CEN_pin0> IOSTANDARD = LVCMOS33;

Net fpga_0_FLASH_16Mx8_emc_ben_gnd_pin LOC=c17;

Net fpga_0_FLASH_16Mx8_emc_ben_gnd_pin IOSTANDARD = LVCMOS33;

Uart16550

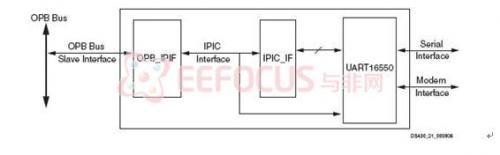

本系统使用RS232-DTE与GPS模块连接,比特率为4800,对GPS数据的接收采用轮询方式;RS232-DCE与GSM模块连接,比特率为115200,对GSM信息的接收也采用轮询方式。MicroBlaze一次只对32位数据进行处理,而DTE与DCE每次只串行传送一位数据,而OPB16550串口实现了串行数据与并行数据的转化,Uart16550与系统总线的连接模式如下图:

引脚约束为:

Net fpga_0_RS232_DCE_sin_pin LOC=R7;

Net fpga_0_RS232_DCE_sin_pin IOSTANDARD = LVCMOS33;

Net fpga_0_RS232_DCE_sout_pin LOC=M14;

Net fpga_0_RS232_DCE_sout_pin IOSTANDARD = LVCMOS33;

Net fpga_0_RS232_DTE_sin_pin LOC=U8;

Net fpga_0_RS232_DTE_sin_pin IOSTANDARD = LVCMOS33;

Net fpga_0_RS232_DTE_sout_pin LOC=M13;

Net fpga_0_RS232_DTE_sout_pin

定位追踪 GPS Spartan-3E 射频 CC2420 UART 相关文章:

- 基于GPS和GPRS的小型追踪器设计方案(05-20)

- 基于GPSOne技术的个人定位终端(07-30)

- 2010年中国(成都)电子展胜利闭幕(08-15)

- 基于DSP的车载GPS/DR组合导航系统硬件设计(09-13)

- ARM-Linux平台下GPS信号的采集与处理研究(07-25)

- 基于MiniGUI的GPS导航定位系统设计(02-20)