采用Zynq SoC实现Power-Fingerprinting网络安全性

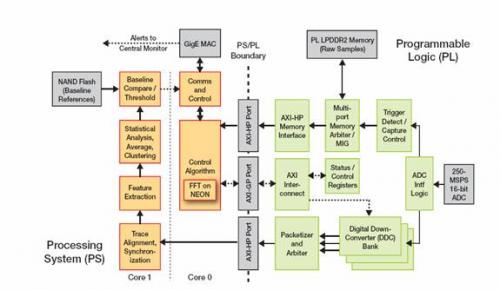

毋庸置疑,DDC 是可编程逻辑实现方式的理想之选,因为 DDC 内核被纳为 SoM 开发套件的一部分 ,并且 DDC 组的合并计算要求可超过 20 gigaflop。DDC 组是入侵检测算法的一部分,其必须实时运行才能避免错失入侵事件。DDC 组的抽取输出可传递到 ARM 处理器,以便在软件中进一步处理入侵算法。虽然输出速率可达 2 Gbps,但却能被高性能 AXI 端口轻松处理,这些端口可将 Zynq SoC 的可编程逻辑连接到 ARM 内存。

通过使用应用编程接口的通用型 AXI 总线从 ARM 处理器对 DDC 内核进行配置。API 允许在 ARM 上运行的软件动态更改 DDC 参数,以便中心频率、带宽和抽取速率方面的更新可以根据控制算法命令实时进行。

由于通过转移 DDC 负载而显著降低数据速率,因而以 766 MHz 频率运行的两个 ARM 中央处理单元 (CPU) 具有足够的性能来支持后续处理进程。由于该设计在对称多处理 (SMP) 模式中采用 Linux 操作系统,因而能分离两个 ARM CPU 内核之间的处理,一个处理入侵检测,而另一个处理控制算法以及可与中央监控站的通信接口。此外,Linux 还具备稳健可靠的网络支持和安全性,可允许进行远程网络管理(这正是大部分安装所必需的),同时禁用任何在不久的将来可能会出现漏洞的不必要特性。

控制处理需要原始 ADC 样本的大型相邻模块。一个需注意事项是将原始 ADC 样本通过高性能 AXI 端口从 ADC 接口逻辑直接串流到 ARM 内存。但是,为了保留处理器系统的内存带宽以用于处理算法,我们反而选择了将 ADC 数据缓冲在可编程逻辑专用的物理内存中。这种内存具有确定性的带宽并确保相邻 ADC 样本的大量集合,而不会干扰 ARM CPU 的操作。

可将从专用可编程逻辑内存中收集的数据通过其中一个高性能 AXI 端口传输到 ARM,以保持低延迟并最大限度降低 ARM CPU 的开销。我们使用多端口内存仲裁器提供了一个收集端口和一个检索端口。这种方法可提供在收集样本的同时并发检索样本所需的仲裁,从而进一步减少延迟。

在对新分区的设计进行分析时,控制算法不会足够频繁地运行来充分地保持检测精度。性能瓶颈在很大程度上归因于 16,000 点 FFT 运算。借助赛灵思的 Vivado Design Suite 提供的 FFT IP 核,FFT 的性能将远远足够,因为其设计为实时运行。但是,对可编程逻辑的其他资源需求将强制设计利用更大的 Zynq 7030 器件。

幸运的是,来自 Project Ne10 的开源 Ne10 库提供了专为 ARM 的 NEON 架构扩展优化的 FFT 功能,这加速了通用浮点和固定点数学运算。尽管来自 Ne10 库的 FFT 功能不会像赛灵思 IP 核那样实时运行,但其可充分地加速控制算法以保持检测精度。

最终的基于 Zynq SoC 的监控设计平台可与基于 PC 的原型相媲美,有时甚至略胜一筹。而且,最终的设计比基于 PC 的设计制造成本明显降低,并且消除了 PC 设计存在的尺寸大、功耗高这两大市场壁垒。相对来说,Zynq SoC 设计在尺寸和功耗方面几乎降低了一个数量级。

PFP Cybersecurity 开发了 Power Fingerprinting 技术来解决在关键设备中检测由于工业物联网趋势而暴增的网络攻击的复杂问题。借助业经验证的技术,出现了如何设计系统以实现技术并同时满足市场需求的问题。借助 Zynq SoC,PFP 技术可在复杂且计算强度大的处理能力需求与低成本、小尺寸、低功耗的市场需求之间取得最佳平衡,从而在商业上具有可行性。

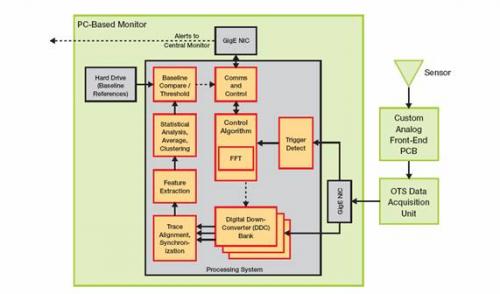

图 1 – 基于PC的监控系统中的模块包含前端模拟、数据采集和处理系统功能。

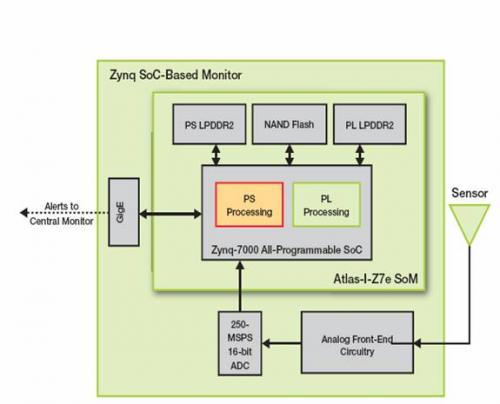

图 2 – 基于Zynq SoC的监控系统是通过iVeia的Atlas-I-Z7e系统级模块构建的。

图 3 – 该图表显示了Zynq SoC的PS和PL模块(包含数据流)的功能分区。

数据采集 Zynq PowerFingerprinting NEON架构 相关文章:

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP和USB的三维感应测井数据采集系统(06-14)

- 多通道同步数据采集及压缩系统(08-12)

- 基于DSP的高速数据采集系统设计方案(06-25)