利用FPGA夹层卡实现I/O设计灵活性

面对似乎层出不穷的新 I/O 标准,目前嵌入式系统设计人员继续依靠 FPGA 来部署系统日益重要的外部 I/O 接口,这点丝毫不足为奇。FPGA 可提供大量可配置的 I/O,能在适当 IP 基础上支持几乎无限多种高度复杂的 I/O 标准。设计人员还能用 FPGA 执行流内 (in-stream) 数据处理,甚至以数千兆位级信号传输速率和带宽运行的协议。

FPGA 能够灵活适应 I/O 要求变化。FPGA 经重配置(除了替换物理 I/O 组件和连接器外基本无需其它更改)后,便可部署新的协议。如果 I/O 不是实施在夹层模块上的话,那么这就意味着需要修改板的设计。为了避免设计更改造成成本和工作量的增加,设计人员以前一直采用 PCI 夹层卡 (PMC) 和交换夹层卡 (XMC) 标准。不过,上述标准是十多年前针对单板计算机 (SBC) 等通用解决方案而并非 FPGA 开发的。2008 年 7 月,情况发生了变化,美国国家标准学会 (ANSI) 批准发布了 VITA 57 FPGA 夹层卡 (FMC) 标准。

FMC 标准由包括 FPGA 厂商和最终用户在内的公司联盟开发,旨在为基础板(载卡)上的 FPGA 提供标准的夹层卡尺寸、连接器和模块接口。通过这种方式将 I/O 接口与 FPGA 分离,不仅简化了 I/O 接口模块设计,同时还最大化了载卡的重复利用率。与使用 PCI、PCI-X、PCIe 或 Serial RapidIO 等复杂接口连接到载卡的 PMC 和 XMC 标准不同,FMC 标准只要求核心 I/O收发器电路直接连接至载卡上的 FPGA 即可。

这样做能够提高效率,进而带来诸多显著优势:

• 数据吞吐量:支持高达 10 Gb/s 的信号传输速率,夹层卡和载卡之间潜在总带宽达 40 Gb/s。

• 时延:消除了协议开销,避免了时延问题,确保确定性数据交付。

• 简化设计:无需了解 PCI、PCI Express 或 Serial RapidIO 等协议标准的专业技术。

• 系统开销:通过简化系统设计降低了功耗,缩短了工程设计时间,并缩减了IP 核及材料成本。

• 设计重复使用:不管是采用定制的内部板设计还是商用成品 (COTS) 夹层卡或载卡,FMC 标准有助于将现有的 FPGA / 载卡设计重新用到新的 I/O 上,而这只需更换 FMC 模块并对 FPGA 设计略作调整即可。

FMC 标准的亮点

FMC标准定义了单宽度(69 毫米 x 76.5 毫米) 和双宽度(139 毫米 x 76.5 毫米)两种尺寸。单宽度模块支持到载卡的单个连接器。双宽度模块主要面向需要更高带宽、更大前面板空间或较大PCB 面积的应用,支持多达两个连接器。FMC 标准提供两种尺寸,能够更加灵活地根据空间、I/O 要求或者这两者的要求对板进行精心优化。图 1 给出了 FMC 载卡及多种 FMC 夹层卡示意图。

图 1:FMC 载卡和多种 FMC 夹层卡

选定尺寸之后,板设计人员就要在两种不同连接器间做出选择,以用作 FMC 标准到载卡上 FPGA 的接口:一种是具有 160 个引脚的低引脚数 (LPC) 连接器,另一种则是具有 400 个引脚的高引脚数 (HPC) 连接器。这两种连接器均支持高达 2 Gb/s 的单端和差分信号传输速率,且到 FPGA 串行连接器的信号传输速率高达 10 Gb/s。

除了 68 个用户定义的单端信号或者 34 个用户定义的差分对外,LPC 连接器还提供了 1 个串行收发器对、时钟、JTAG 接口和 1 个作为基础智能平台管理接口 (IPMI) 命令可选支持的 I2C 接口。而 HPC 连接器则提供了 160 个用户定义的单端信号(或者 80 个用户定义的差分对)、10 个串行收发器对以及更多时钟。

HPC 和 LPC 连接器都使用相同的机械式连接器,唯一的差别在于实际上移植哪些信号,因此采用 LPC 连接器的卡也能插入 HPC 处,而且只要适当设计,HPC 卡在插入 LPC 处时还能提供诸多派生功能。

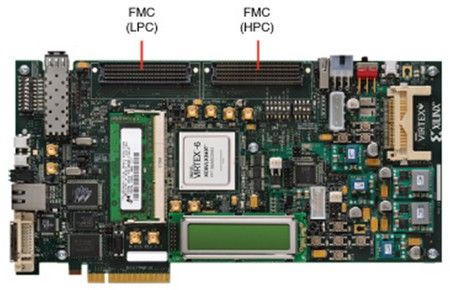

图 2 显示的是赛灵思的一个实例板,该板采用了 Virtex'-6 FPGA和两种 FMC连接器(一个 LPC 和一个 HPC)。

图 2:ML605 评估板

FMC 标准支持众多现有的业界标准载卡尺寸,包括 VME、CompactPCI、VXS、VPX、VPX-REDI、CompactPCI Express、AdvancedTCA 以及 AMC 等。FMC标准还定义了一系列环境配置,包括低成本商用级尺寸乃至强化的传导式散热选项。

FMC的市场机会

将 FMC 标准和 FPGA 的多样性结合在一起,可带来一系列有趣的市场和应用商机。航空与国防、医疗、工业、电信、视频及其它等市场通常高度依靠 FPGA来实现其数字信号处理 (DSP) 性价比优势,并满足各种不同的 I/O 要求。不过,过去每个市场及给定市场中的每个应用都需要不同的板设计。

FMC 标准的出现将板设计进行了模块化,分为处理引擎(载卡)和 I/O 引擎(FMC 模块)两大部分。设计人员现在能重复利用单个载卡(包括一个或多个FPGA 以及适当数量和类

- 基于FPGA的可配置判决反馈均衡器的设计(06-05)

- BLDC电机设计的新架构:可配置混合控制器(05-14)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)