基于Java平台的FPGA嵌入式系统设计

1. 概述

传 统的嵌入式系统设计的主要目标是找到一种优化的体系结构来完成单一的,特定的功能。对这样的系统来说,ASIC和核心处理器是作为特别的构件模块加以考虑 的:设计者根据应用的要求选择适当的ASIC,根据给定的性能要求比如处理器主频,系统稳定性,以及对功耗的要求等选用适当的处理器内核。

然而,在当今移动通信已经进入每个人的生活的今天,现在的嵌入式系统比如PDA等已经不同于传统意义上的嵌入式系统了,它们有自己的独特特点。客观需要要求它们能够支持多种应用功能如网页浏览,播放音频/视频文件,以及进行无线网络通信等。

这样看来,传统的设计思路因为只面向单一的应用,无法满足多应用嵌入式系统的需求。而解决这一问题的良好途径便是向嵌入式系统引入可编程能力,以使得系统能够根据用户的不同要求实现对不同应用的支持。

为了向系统中引入可编程能力,我们考虑在系统中嵌入FPGA,因为FPGA具有下列特点,使得它成为我们的首选:

1.现在的FPGA的处理能力和逻辑容量已经接近于专用ASIC,功耗也比较低,能够满足我们系统设计的要求;

2.由于FPGA具有的可重编程能力,使用了FPGA的嵌入式系统能够满足各种不同的应用要求;

从 嵌入式系统管理的角度来说,对网络通信的支持也是很有必要的,也是很有特色的一个应用,因为它使得从远端服务器下载新的应用程序并在本地运行成为可能。为 实现对这个功能的支持,我们采用Java作为软件平台。因为Java运行在Java虚拟机之上,它能够下载并执行新的应用程序代码,并且无需在下载后重新 启动系统。

综上所述,这个新的嵌入式系统是基于Java的,有一个FPGA和标准处理器相连。我们通过网络下载Java代码和可以对 FPGA进行编程的比特流。该系统也支持对FPGA的动态重新配置。为了实现硬件(FPGA)和软件(Java应用程序代码)之间的通信,又定义了一组本 地API,以使得从Java应用层能够访问到底层的硬件。为了调用这些本地API,采用了Java本地接口(JNI)。在本文中,将一些Java函数 (Javamethod)用FPGA可编程硬件来实现,称之为硬件方法(HW method)。

2. 系统设计

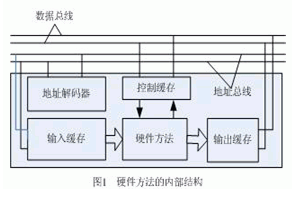

实现一个Java函数功能的对应的硬件方法实现的逻辑结构图如图1所示。

输入缓存和输出缓存分别用来接收输入参数和存储输出结果。控制缓存用于对硬件方法的控制和检测,比如向硬件方法发出启动指令,检查其所处的状态并判断操作是否完成等。该模块中的所有缓存都映射到处理器物理地址空间中,处理器可以使用正常的读写指令完成对这些缓存的访问。

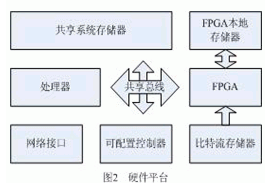

图2是该嵌入式系统的硬件平台,由一个标准处理器,一个FPGA和一个系统存储单元构成。它们之间通过共享的系统总线连接在一起。

当 处理器向一个硬件方法发出读写操作指令时,该硬件方法在其自己的地址解码器的帮助下向数据总线上发送对应的响应信号。在这里,我们可以认为是处理器发起的 硬件/软件通信指令,而FPGA则是作为一个从属单元做出回应。因为在处理器发起初始指令后,就由可配置管理器来负责管理FPGA编程。这样一来,就实现 了处理器和FPGA的并行运行。

如图3所示,我们选择Java作为软件平台,并且装载了一个嵌入式操作系统为Java实时应用程序提供基本的服务,比如线程和其它硬件管理等。

通过系统管理器,可以从远程服务器下载Java应用程序。系统管理器主要实现了下面3种协议:

1. 应用程序代码(包括可对FPGA进行编程的比特流)下载协议;

2. 用于远程管理的系统维护相关的协议;

3. 控制对嵌入式系统访问权限的认证协议。

系统管理器包括基于socket连接的客户端类加载器。远端应用程序可以下载到本地并按照下面的过程执行:

1. 完成认证过程,系统进入管理模式;

2. 下载应用程序代码,完成系统初始化,比如加载FPGA可编程比特流到相应的存储单元;

3. 执行新的应用程序。

在该系统中,为了简化起见,预先映射硬件方法地址到确定的系统物理存储区,目的是为了寻址操作的方便快捷。

由于我们使用了Java软件平台,应用程序就无法直接访问底层的硬件。这就是说,运行在处理器Java虚拟机上的应用程序不能直接访问映射到FPGA中硬件方法的缓存区域。为解决这个问题,理论上可以采用下面两种方法:

1. 修改Java虚拟机,使其具有对处理器物理地址的直接访问能力;

2. 单独设计一种Java本地接口(JNI),使得应用程序通过该接口提供的功能实现对硬件方法映射到的物理地址的访问。

尽 管第一种方案的效率较高,并且没有引入额外开销,但是修改Java虚拟机内核是相当繁杂的工作,同时也可能会引起潜在的系统不稳定。第二种方案虽

- 嵌入式设备Java平台及其虚拟机技术(03-21)

- 基于安卓的非标准驱动程序设计(10-03)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)