CPLD/FPGA在数字通信系统的应用

时间:06-05

来源:互联网

点击:

信号采集数据.

if(!reset)

dcinreg=1;

else

dcinreg=dcin;

always@(posedge clk)//采集是否有效.

if (reset)

datareg=0;

else if(!dcin)

datareg=data_in;

always@(posedge clk)//码字在数据向量采集后一个时钟周期计算得到.

if (reset)

dcout=1;

else

dcout=dcinreg;

always@(posedge clk)//码字输出是否有效.

if(reset)

code_out =0;

else

code_out={c0,c1,c2,c3,c4,c5,c6};

endmodule

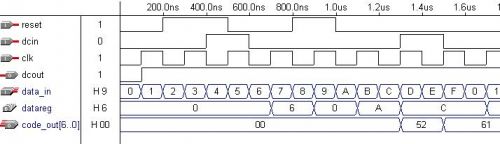

该源程序经过编译和仿真,时序图如下所示,得到结果符合系统功能要求

本设计使用的芯片为MAX3000A系列EPM3032ALC44-4,芯片的输入输出端口的设计采用D触发器组来缓存数据,确保采集数据向量和发送的码字稳定,并于时钟信号严格同步。

4 结束语

本文通过介绍汉明码的编码原理,进而用Verilog HDL进行汉明码编码器的设计,并通过时序仿真波形图进行逻辑分析,结果符合实际情况.而Verilog HDL有着类似C语言的编程风格,易于学习和掌握,与传统的原理图设计方法相比较, Verilog HDL更适合于规模日益增大的数字系统. Verilog HDL等硬件描述语言进行数字系统的设计是EDA发展的趋势,在数字系统的设计中有着广泛的空间.

Verilog CPLD FPGA HDL 汉明码 相关文章:

- 基于SystemC 的系统验证研究和应用(08-10)

- SoC:IP是新的抽象(10-24)

- 从传统电路检查到先进可靠性验证的最佳实践(07-03)

- 基于Verilog语言的等精度频率计设计(08-14)

- Verilog串口通讯设计(06-06)

- Verilog HDL 设计模拟(06-06)