基于FPGA的DDS IP核设计及仿真

SOPC(System on a Programmable Chip,片上可编程系统)是Altera公司提出的一种灵活、高效的SOC解决方案。它将处理器、存储器、I/O接口、LVDS、CDR等系统设计需要的功能模块集成到一个可编程逻辑器件上,构建一个可编程的片上系统。它具有灵活的设计方式,软硬件可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。SOPC的核心器件FPGA已经发展成一种实用技术,让系统设计者把开发新产品的时间和风险降到最小。最重要的是,具有现场可编程性的FPGA延长了产品在市场的存在时间,从而减小了被新一代同类产品淘汰的威胁。本文以全数字频率合成技术——直接数字频率合成技术(DDS)为理论依据,利用先进的片上可编程技术在一块FPGA芯片上实现了DDS IP核功能,并将该DDS IP核与Nios II处理器核以及其它外设封装到一起,做成一个片上系统,大大简化了电路的设计难度。

1 DDS的基本原理

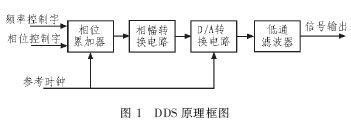

DDS(直接数字频率合成)是把一系列数字形式的信号通过DAC转换成模拟量形式的信号的合成技术。图1是DDS的原理框图。

图中参考时钟由一个高稳定的晶体振荡器产生,来同步整个频率合成器的各个组成部分。相位累加器包含一个加法器和一个相位寄存器,每来一个时钟脉冲,加法器就将频率控制字与相位寄存器中的数据相加。相位寄存器可以将加法器在上一个时钟作用后产生的新相位数据反馈到加法器的输入端,使加法器在下一个时钟的作用下继续将相位数据与频率控制字相加。这样,相位累加器在参考时钟的作用下进行线性相位累加。当相位累加器达到上限时,就会产生一次溢出,完成一个周期性的动作,这个周期就是合成信号的一个周期,累加器的溢出频率也就是DDS的合成信号频率。相位控制字用来设定相位累加器初始时刻的相位值,相位累加器运行过程中并不参与加法运算。

在参考时钟的控制下,相位累加器受频率控制字控制输出相位数据,用相位累加器输出的相位数据作为相位/振幅变转换电路的地址对其进行查找。相位/振幅转换电路将相位累加器的相位信息映射成数字振幅信息,将数字振幅数据再经过D/A转换器得到相应的阶梯波,最后经低通滤波器对阶梯波进行平滑处理,即可得到由频率控制字决定的连续变化的输出波形。

2 DDS IP核的设计

根据DDS的基本理论,将DDS IP核分为相位累加模块、DDS控制模块、波形选择模块、波形LPM_ROM模块。

2.1 相位累加器模块的设计

相位累加器是DDS IP核设计的关键,它决定着频率的范围和分辨率,本设计采用的32位的二进制累加器,取累加器的高十位作为查表(相幅转换电路)的地址值。为提高系统的速率,在累加器的设计中采用了7级流水线技术。其中采用Verilog HDL描述的第一级流水线实现的关键代码如下:

类似,可完成其余流水线的设计。

2.2 DDS控制模块设计

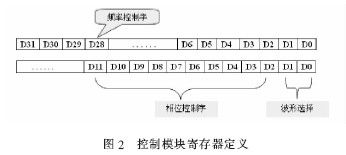

为将设计的DDS IP能够集成到SOPC系统中,本设计在DDS IP的控制模块定义了两个32位的寄存器,如图2所示。一个是频率控制字寄存器,用来保存上位机软件发来的频率控制字;另一个寄存器用来保存相位控制字和波形选择位,其中低2位D1、D0用于波形选择,D2到D11用于保存相位控制字,其余高位保留未用。

2.3 波形存储器ROM的设计

该模块完成相位/振幅转换电路的功能。在本设计中,要求DDS IP能输出正弦波、方波,三角波、锯齿波。可以用FPGA内部的LPM_ROM模块制作4张ROM表,分别存储4个波形的数据。实际上,由于方波和三角波是实现算法相对简单,为了节省资源,本系统直接用Verilog HDL描述其功能。实现产生方波信号的关键代码如下:

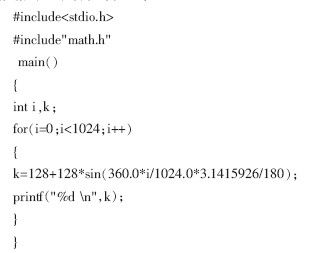

正弦波、锯齿波的产生是利用FPGA的LPM_ROM模块来实现。为了对ROM模块内的数据进行加载,首先应建立相应的*.mif(Memory Initial File)文件。它可以用C语言编写源程序,得到对应波形的数据,生成*.mif文件,如生成正弦波形数据的C语言程序如下:

然后在Quartus II里新建.mif文件,把用命令字符生成的.mif文件的内容粘贴到Quartus II里新建的存储器初值设定(.mif)文件里面,如图3所示。再用Quartus II软件定制LPM_ROM,并加载刚才建立的.mif波形文件初始化ROM。

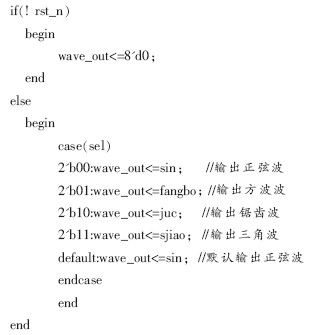

2.4 波形选择模块的设计

该模块根据DDS控制模块的输出控制信号决定选择哪一种波形输出,关键代码如下。

2.5 DDS顶层设计

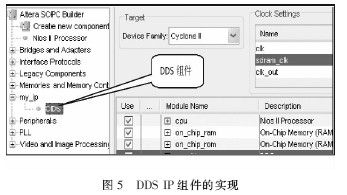

顶层设计将前面实现的各功能模块作为底层元件例化调用,完成整个DDS IP核设计。对DDS IP核进行验证后,利用SOPC Builder的组件编辑器对其进行自定义组件的开发,为后续SOPC硬件系统的搭建奠定基础。

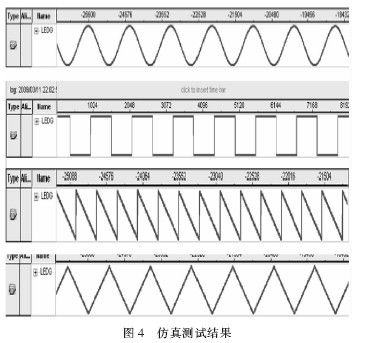

2.6 DDS IP的仿真测试及自定义组件的生成

Altera公司的Quartus II软件具有嵌入式逻辑分析仪SignalTap II,它提供了一种对器件进行实时测试的手段。SignalTapII嵌入式逻辑分析仪可以随设计文件一起下载到目标芯片中,用以捕捉目标芯片中设计者感兴趣的信号节点处的信息,而不影响芯片的正常工作。

SignalTapII将测得的样本信号暂存于目标器件的片内RAM中,然后通过器件的JTAG端口和编程线将采得的信息传出,送入计算机进行分析。图4是采用SignalTapII嵌入式逻辑分析仪的仿真测试结果。

由于SOPC的开发是以组件(IP核)为基础的,为了将前面设计的DDS IP核挂到Avalon总线上,将其封装成为SOPCBuilder自定义的组件,如图5所示。这样,在SOPC硬件系统开发中,DDS IP就如同SOPC Builder里的标准组件一样,可以被集成到具体的应用系统中。

2.7 SOPC硬件系统配置

在SOPC硬件系统的开发中,除了集成前面设计的DDSIP外,还集成了诸多SOPC Builder组件库中的标准组件,主要有Nios II CPU、UAR T、JTAG UART、定时器、Avalon三态总线桥、片上存储器、片外存储器、PIO、SDRAM控制器、FLASH控制器等,如图6所示。

- 基于AD9911频率源的设计与实现(10-15)

- 使用AD9850直接数字频率合成(DDS) IC (08-22)

- 基于MSP430F449的超低功耗高精度转达液位仪设计(07-09)

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于Zynq的OLED驱动设计(10-04)

- 如何仿真IP核(06-06)