如何仿真IP核

时间:06-06

来源:互联网

点击:

IP核生成文件:(Xilinx/Altera 同)

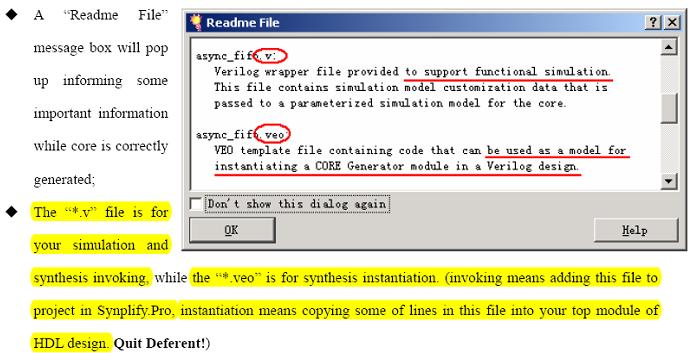

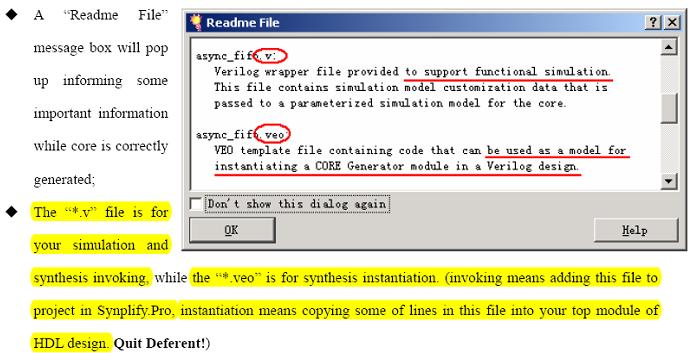

IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit->Language Template->COREGEN 中找到verilog/VHDL 的例化方式)。asyn_fifo.v 是该核的行为模型,主要调用了 xilinx 行为模型库的模块,仿真时该文件也要加入工程。(在 ISE中点中该核,在对应的 processes 窗口中运行“ View Verilog Functional Model ”即可查看该 .v 文件)。如下图所示。

1. 在 ISE 集成环境中仿真 IP核

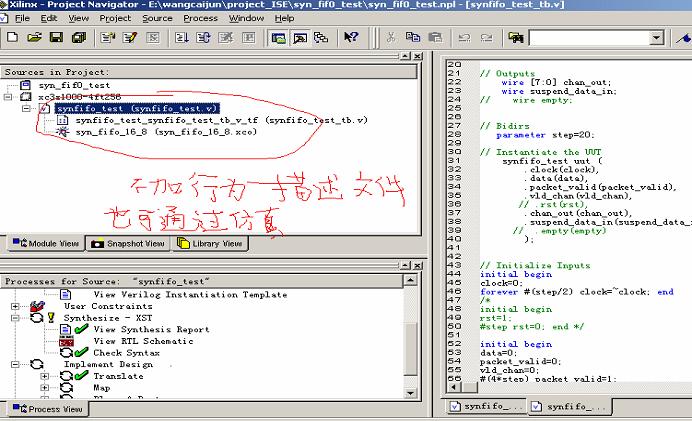

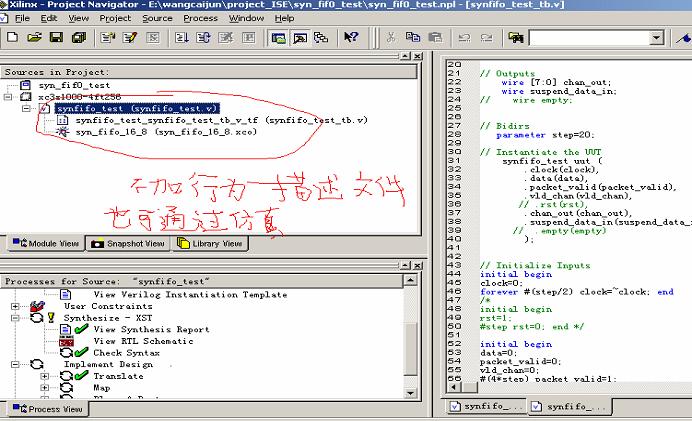

IP 核应该在新建的工程中进行仿真与例化;在原工程中可以例化使用,但好像不能直接对它加 testbench 后进行仿真。如下两图所示。

图 1:直接在工程中对 ip核加 testbench 仿真时出错

图 2:新建工程单独对 ip核仿真

2.在 modelsim中仿真 ip 核

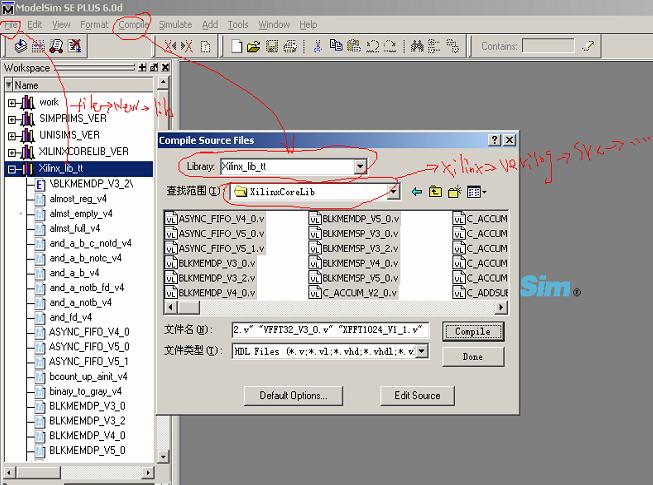

a.在 modelsim中编译库(Xiliinx)

(1)在$Modeltech_6.0d/Xilinx_lib_tt下新建文件夹 Xilinx_lib($代表安装盘符)

(2)打开 Modelsim->File->Change Diriectory,将路径指向刚才新建的文件夹 Xilinx_lib,这样 Xilinx 编译的所有库都将会在该文件夹下。

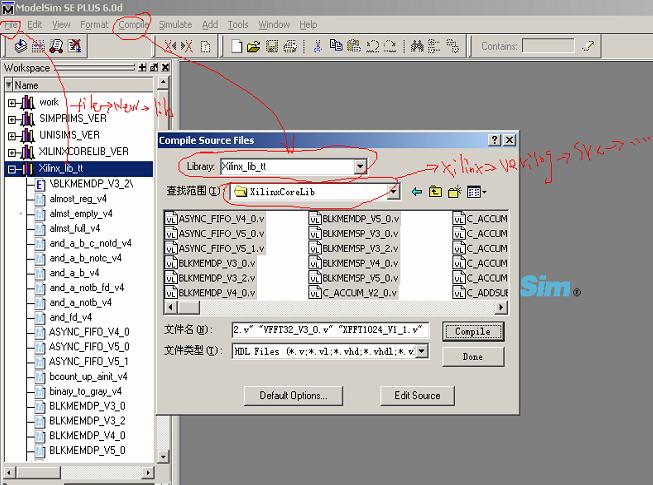

(3)编译 Xilinx 库。在$Xilinx->verilog->src 下有三个库“simprims”,“unisims”和“xilinxcorelib”。在 modelsim 的 workpace 窗口 Library 属性中点右键->new->library(或在File 菜单下 new->libary),输入库名(自定义)如 Xilinx_lib_tt,这样在 workpace library 属性下就可看到 Xilinx_lib_tt 了。

(4)modelsim 中选中 compile,在弹出的对话框中,library 选择刚才新建的 xilinx_lib_tt,查找范围为 xilinx 库($Xilinx/verilog/src/),如 XilinxCoreLib,选中文件编译即可。

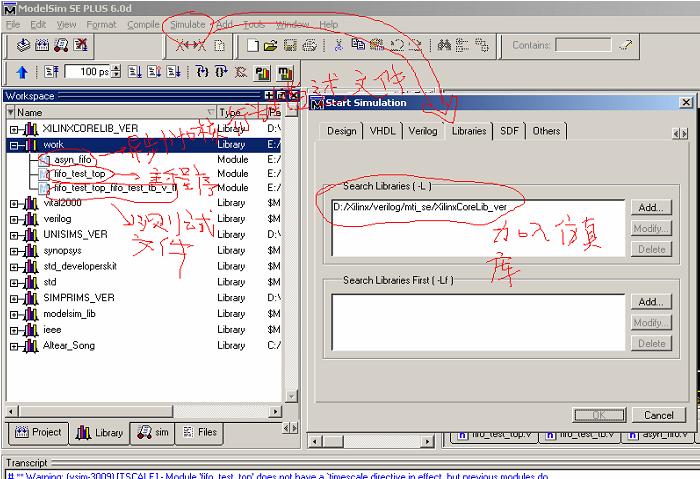

b. 在 modelsim中加载已编译的库

当要在 modelsim 中仿真带有 ip 核的设计时,需要加载对应公司的库才能仿真。仿真Xilinx 公司ip 核时需要在原工程文件中加入 ip 核的行为描述文件(核名>.v)。

如果工程文件直接包含在 xilinx“ XilinxCoreLib” library中,则可直接进行仿真。

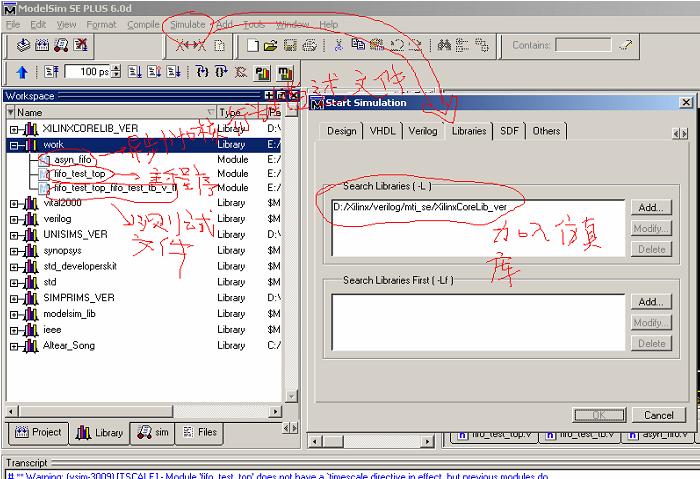

如果工程文件开始默认包含在“work”library 中,则需要在 Simulation->Start Simulation->library 中添加已编译的库,如图示。这样就可以对 ip 核进行仿真了。

aa.在 modelsim中编译 Altera 的库与 Xilinx方法一样

bb.在 modelsim中对 ip 核进行仿真,与 xilinx 一致;首先需要在 modelsim工程中加入设计文件,testbench 文件以及核的行为描述文件(核名>.v);其次,自 File 菜单中更改库路径指向已编译的 altera库路径(否则原先编译的 altera 库将变为不可用,unavailable),这时原先编译的库将变为可用,然后在 Simulation->Start Simulation->library中添加库路径(同Xilinx,图4,图附 3)。

图 3:编译xilinx 库

图 4:加入库进行核仿真

使用 modelsim 进行仿真,相对在 ISE 或 Quartus 中直接调用 modelsim,至少有三个好处:

1.速度快。仿真必然会不停的修改设计,每次修改设计后在 ISE 中需要重新综合后才能调用 modelsim;而在 Quartus 中时间花费更多,它还要等布局布线完成了才能调用。这样每次等待是件很痛苦的事。而直接在 modelsim 里面仿真,修改后只要重新编译即可仿真,速度要快的多。不过这样有一个坏处,那就是设计不一定是可综合的。但只要我们编程时时刻遵循可综合设计规则,培养良好的编程风格,这个缺点影响可减到最低。

2.调试方便。在 ISE/Quartus 中调用 modelsim仿真只能看到输入输出信 号,而对于设计的中间信号/变量,特别是IP核的内部信号/变量无法观测。而在modelsim中直接仿真可以观测设计中出现的任何信号/变量无和 ip 核内的任何信号/变量,这样我们设计的数据流向就可以很清楚的表示出来,还可以检测不同编程方式的处理效果,极大的方便了调试。

3.修改参数方便。在 modelsim中仿真 ip 核时需要将该 ip 核的行为描述文件加入到工程中去。修改该行为描述文件中 ip 核的参数可以方便的更改 ip 核特性。

附 A:在 ISE/Quartus中直接调用 modelsim。

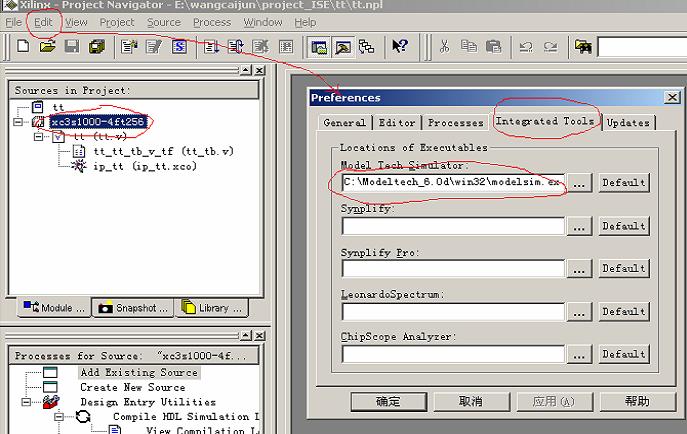

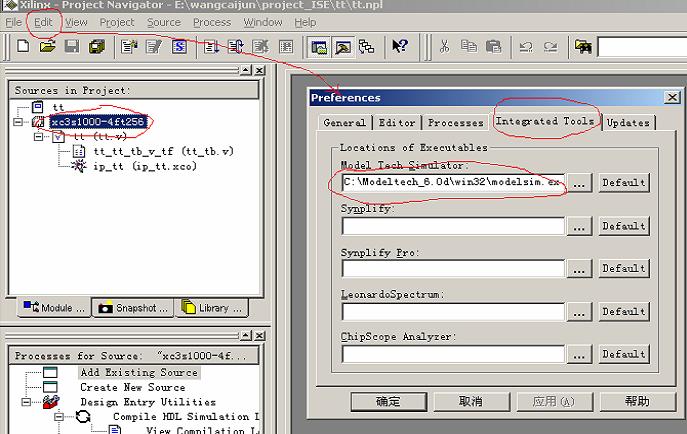

a.先安装 ISE,再安装 modelsim,则 modelsim会自动嵌入到 ISE 中去,如图附 1。ISE集成环境下:Edit->Preferences->Integrated Tools可以设置常用的第三方仿真,综合工具。

图附 A1:ISE 中调用 modelsim

b.直接在 ISE

IP核生成器生成 ip 后有两个文件对我们比较有用,假设生成了一个 asyn_fifo 的核,则asyn_fifo.veo 给出了例化该核方式(或者在 Edit->Language Template->COREGEN 中找到verilog/VHDL 的例化方式)。asyn_fifo.v 是该核的行为模型,主要调用了 xilinx 行为模型库的模块,仿真时该文件也要加入工程。(在 ISE中点中该核,在对应的 processes 窗口中运行“ View Verilog Functional Model ”即可查看该 .v 文件)。如下图所示。

1. 在 ISE 集成环境中仿真 IP核

IP 核应该在新建的工程中进行仿真与例化;在原工程中可以例化使用,但好像不能直接对它加 testbench 后进行仿真。如下两图所示。

图 1:直接在工程中对 ip核加 testbench 仿真时出错

图 2:新建工程单独对 ip核仿真

2.在 modelsim中仿真 ip 核

a.在 modelsim中编译库(Xiliinx)

(1)在$Modeltech_6.0d/Xilinx_lib_tt下新建文件夹 Xilinx_lib($代表安装盘符)

(2)打开 Modelsim->File->Change Diriectory,将路径指向刚才新建的文件夹 Xilinx_lib,这样 Xilinx 编译的所有库都将会在该文件夹下。

(3)编译 Xilinx 库。在$Xilinx->verilog->src 下有三个库“simprims”,“unisims”和“xilinxcorelib”。在 modelsim 的 workpace 窗口 Library 属性中点右键->new->library(或在File 菜单下 new->libary),输入库名(自定义)如 Xilinx_lib_tt,这样在 workpace library 属性下就可看到 Xilinx_lib_tt 了。

(4)modelsim 中选中 compile,在弹出的对话框中,library 选择刚才新建的 xilinx_lib_tt,查找范围为 xilinx 库($Xilinx/verilog/src/),如 XilinxCoreLib,选中文件编译即可。

b. 在 modelsim中加载已编译的库

当要在 modelsim 中仿真带有 ip 核的设计时,需要加载对应公司的库才能仿真。仿真Xilinx 公司ip 核时需要在原工程文件中加入 ip 核的行为描述文件(核名>.v)。

如果工程文件直接包含在 xilinx“ XilinxCoreLib” library中,则可直接进行仿真。

如果工程文件开始默认包含在“work”library 中,则需要在 Simulation->Start Simulation->library 中添加已编译的库,如图示。这样就可以对 ip 核进行仿真了。

aa.在 modelsim中编译 Altera 的库与 Xilinx方法一样

bb.在 modelsim中对 ip 核进行仿真,与 xilinx 一致;首先需要在 modelsim工程中加入设计文件,testbench 文件以及核的行为描述文件(核名>.v);其次,自 File 菜单中更改库路径指向已编译的 altera库路径(否则原先编译的 altera 库将变为不可用,unavailable),这时原先编译的库将变为可用,然后在 Simulation->Start Simulation->library中添加库路径(同Xilinx,图4,图附 3)。

图 3:编译xilinx 库

图 4:加入库进行核仿真

使用 modelsim 进行仿真,相对在 ISE 或 Quartus 中直接调用 modelsim,至少有三个好处:

1.速度快。仿真必然会不停的修改设计,每次修改设计后在 ISE 中需要重新综合后才能调用 modelsim;而在 Quartus 中时间花费更多,它还要等布局布线完成了才能调用。这样每次等待是件很痛苦的事。而直接在 modelsim 里面仿真,修改后只要重新编译即可仿真,速度要快的多。不过这样有一个坏处,那就是设计不一定是可综合的。但只要我们编程时时刻遵循可综合设计规则,培养良好的编程风格,这个缺点影响可减到最低。

2.调试方便。在 ISE/Quartus 中调用 modelsim仿真只能看到输入输出信 号,而对于设计的中间信号/变量,特别是IP核的内部信号/变量无法观测。而在modelsim中直接仿真可以观测设计中出现的任何信号/变量无和 ip 核内的任何信号/变量,这样我们设计的数据流向就可以很清楚的表示出来,还可以检测不同编程方式的处理效果,极大的方便了调试。

3.修改参数方便。在 modelsim中仿真 ip 核时需要将该 ip 核的行为描述文件加入到工程中去。修改该行为描述文件中 ip 核的参数可以方便的更改 ip 核特性。

附 A:在 ISE/Quartus中直接调用 modelsim。

a.先安装 ISE,再安装 modelsim,则 modelsim会自动嵌入到 ISE 中去,如图附 1。ISE集成环境下:Edit->Preferences->Integrated Tools可以设置常用的第三方仿真,综合工具。

图附 A1:ISE 中调用 modelsim

b.直接在 ISE

IP核 相关文章:

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于Zynq的OLED驱动设计(10-04)

- LabVIEW FPGA代码模块设计(IP核)(06-06)

- IP核互连策略及规范(06-06)

- 如何实现IP核心网的QoS(06-06)

- 通信接口免费IP核的应用(06-05)