CPLD/FPGA在数字通信系统的应用

1 引言

近年来,由于微电子学和计算机技术的迅速发展,给EDA技术行业带来了巨大的变化。 HDL(hardware description language)硬件描述语言是一种描述电路行为的语言,是设计者和EDA工具的界面,设计者通过HDL描述自己的设计对象。目前比较流行的HDL主要有Verilog HDL、VHDL、AHDL等,其中Verilog HDL和VHDL因为适合标准化的方面而最终成为IEEE标准。但是Verilog HDL比VHDL更容易掌握,并且完成同一功能的Verilog HDL条数一般仅为VHDL的1/3,Verilog HDL 善于描述更低层设计包括结构级和物理层的设计,而VHDL设计技术很不直观,设计人员需要有EDA编程基础,经过半年左右的专业培训才能掌握,所以用Verilog HDL的优越性高一些。作为学习HDL设计方法的入门和基础,是一种值得大力推广的硬件描述语言。

2 汉明码的基本原理

汉明码是一种能够纠正一个错码且编码效率较高的线性码。在偶数监督码中,无论信息位有多少,监督位只有一位,它使码组中“1”的个数为偶数,在接收端解码的时候,实际就是计算S= an-1⊕ an-2⊕。。。。⊕a0,若S=0,就认为无错,若S=1,就认为有错。上式称为监督关系式,S为校正子。由于校正子S的取值只有这样两种,它只能代表有错和无错两种信息,而不能指出错码的位置。如果监督位增加一位,即变成两位,可能有四种组合:00,01,10,11,故能表示四种不同虚报许,若用其中一种表示无错,则其余三种就有可能用来指示一位错码 的3种不同位置,同理,r个监督关系式就能指示一位错码的(2r-1)个可能位置.一般说来,若码长为n,信息位数为k,则监督位数r=n-k.如果希望用r个监督位够造出r个监督关系式来指示一位错码的n种可能位置,则要求

2r-1≥n ; 2r≥k+r+1;

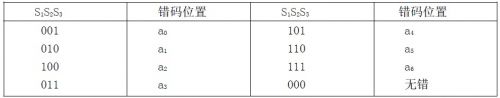

设分组码(n, k)中k=4.为纠正一位错码,要求监督位数r≥3.若取r=3,则n= k+r=7.我们用a6a5a4…a0表示7个码元,用S1S2S3表示三个监督关系式中的校正子,则S1S2S3的值与错码位置的关系如下表.

由表可知,仅当一错码位置在 a2 a4 a5 a6时,校正子S1为1,否则S1为0.这就意味着a2 a4 a5 和a6 构成偶数监督关系

S1= a2 ⊕ a4⊕ a5⊕a6

同理

S2= a1 ⊕ a3⊕a5⊕a6

S3= a0 ⊕a3⊕a4⊕a6

在发送端编码时,信息位a6 a5 a4和 a3 的值决定于输入信号,因此它们是随机的。监督位a2 a1 和 a0 应根据信息位的取值按监督关系来确定,即监督位应使上三式中的S1S2S3的值为零。

a2⊕a4⊕a5⊕a6=0

a1⊕a3⊕a5⊕a6 =0

a0⊕a3⊕a4⊕a6=0

有上式移项运算,解出监督位

a2= a4⊕a5⊕a6

a1= a3⊕a5⊕a6

a0= a3⊕a4⊕a6

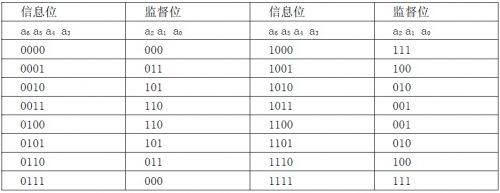

根给定信息位后,可直接计算出监督位,如下表

接收到每个码组后,先按上式计算出S1 S2 和S3 ,再按上表判断错码情况。例如,若接收码组为0000110,则计算的S1 =1,S2 =1,S3 =0,由于S1 S2 S3 等于110,可知a5位有一错码。上述方法构成的码称为汉明码。表Ⅱ所列的(7,4)汉明码最小码距是d0=3,这种码能纠正一个错码或检测两个错码。汉明码的编码效率等于k/n=(2r-1-r)/( 2r-1)=1-r/(2r-1)=1-r/n.当n很大时,则编码效率接近1。可见汉明码是一种高效码。

3 编码电路的实现

本设计的开发平台是MAX+PLUSⅡ[4], MAX+PLUSⅡ是Altra公司专为本公司生产的PLD的研制和应用开发的软件它的突出特点在于其强大的综合能力和布局布线能力,另外还具有适用范围广、器件结构独立、通用性好、兼容性好、集成度与自动化程度高以及易学易用的特点.

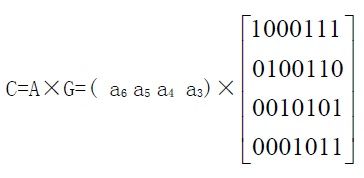

编码器设计的特点是使用了矩阵的乘法,假设A是输入至编码器的数据向量,G是矩阵乘法的发生矩阵,C是汉明码码字,那么根据矩阵乘法计算得到汉明码字。

程序编写如下

module bianma(clk,reset,data_in,dcin,code_out,dcout);

input clk,reset;//时钟和复位信号.

input[3:0] data_in;//输入数据变量,位宽为4bit.

input dcin;//输入有效控制信号,定义1表无效,编码器不输出码字,定义0表有效.

output[6:0] code_out;//编码器输出,位宽为7bit.

output dcout;//输出有效控制信号,定义1表无效.定义0表有效.

reg[6:0] code_out;

reg dcout;

reg[3:0] datareg;

reg dcinreg;

wire c0=datareg[3];

wire c1=datareg[2];

wire c2=datareg[1];

wire c3=datareg[0];

wire c4=datareg[3]^datareg[2]^datareg[1];

wire c5=datareg[3]^datareg[2]^datareg[0];

wire c6=datareg[3]^datareg[1]^datareg[0];

always@(posedge clk or negedge reset)//根据时钟信号和输入使能

Verilog CPLD FPGA HDL 汉明码 相关文章:

- 基于SystemC 的系统验证研究和应用(08-10)

- SoC:IP是新的抽象(10-24)

- 从传统电路检查到先进可靠性验证的最佳实践(07-03)

- 基于Verilog语言的等精度频率计设计(08-14)

- Verilog串口通讯设计(06-06)

- Verilog HDL 设计模拟(06-06)