基于FPGA的高精度时间数字转换电路的设计与实现

3系统实现及优化

Altera公司提供的 Stratix和 Cyclone系列 FPGA芯片具有嵌入式锁相环( PLL)模块,该模块可对外部时钟进行倍频分频及相移操作,可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制,常用于同步内部器件时钟和外部时钟,使内部工作的时钟频率比外部时钟更高,时钟延迟和时钟偏移昀小,减小或调整时钟到输出(TCO)和建立(TSU)时间,从而提供完整的时钟管理方案。使用 Altera Quartus? II软件无需任何外部器件,就可以调用芯片内部的 PLL来实现相应功能。

该系统时钟管理模块调用 FPGA内部 PLL实现,通过 QuartusII设置参数为:Ratio为倍频/分频因子(Ratio)为 4,输出时钟相移 (Ph) 为 0,输出时钟占空比 (DC)为 50%。

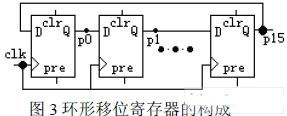

该 TDC电路的时间分辨率取决于环形移位寄存器和编码电路组成的细计数部分,要得到正确的测量数据必须保证对移位寄存器输出状态的正确编码。与 ASIC设计不同,设计者很难预料 EDA软件布局布线(Layout)后的情况,而且各种不同结构和性能的可编程器件布局布线的结果也不尽相同,而且构成移位寄存器的 D触发器的时钟到输出时间(TCO)和 D触发器输入在金属连线上稳定建立的时间(TSU)也存在一定离散性,使得高频移位脉冲(纳秒级)工作下的移位寄存器在状态转换时出现毛刺现象,影响编码正确输出,同时编码器的固有延时特性也限制系统的时间分辨率。该脉宽测量电路系统采用的优化的编码算法,使得高频移位状态下编码输出能准确反映环形移位寄存器上各节点状态,从而保证了该系统的测量精度;移位时钟为 333MHz(周期 3ns)时在 Altera公司 Stratix和 Cyclone系列芯片上实现了编码器的正常工作。

该系统包含了粗记数和细记数两部分电路,粗记数电路在细记数字电路高位输出(图 3中 p15)的上升沿工作。但是由于粗记数电路的延时在被测脉冲( clks)上升沿时可能会造成对输出数据的误读。

为解决误读现象,在输出逻辑模块里加入纠错电路。对被测脉冲 clks延时 clk周期后产生新时钟 clks1,在 clks和 clks1的上升沿同时对 q1和 q0取样并对取样数据进行处理后作为昀终数据输出,从而有效地解决了误读现象。

移位脉冲工作频率即为该测量电路的时间分辨率,通过时钟管理单元可采用不高的外部时钟便可得到很高的测量精度。

3仿真结果和测试数据

为测试该系统的时间分辨率,为基本时间数字转换电路附加特定功能电路,使其具有连续测量时钟脉冲宽度的功能,测试对象是 clks的高电平延续时间。通过改变时钟脉冲源的频率来记录该电路对应的测量数据,从而得到该 TDC电路的时间分辨率。

本文以 QuartusII Web Edition 4.2为软件平台,实验表明,本 TDC设计在 Altera各主流芯品上的时序仿真均能顺利通过。适配 Cyclone EP1C3Q240C8芯片的时序仿真表明,移位时钟为 333M(即分辨率为 3ns),所得到的测试数据输出正确地反映了被测脉冲的宽度,被测脉冲下降沿到测量数据建立的延时为 5ns。

由该 TDC构成的脉宽测量电路在 Cyclone EP1C3Q240C8芯片实现,系统外部时钟 25Mhz,PLL设置倍频因子 8,由 SP1641B信号发生器提供固定的被测脉冲频率 F,时间分辨率 Res的分布如图 4所示,测试数据表明 Res在 4.9-5.1ns之间,理论值为 5ns。

测量和仿真数据表明该电路能达到纳秒级时间分辨率,逻辑资源占用少,可在低密度芯片上实现作为专用测量电路使用,或在高密度芯片上作为功能模块嵌入到特定功能的片上系统(SOC)中;该 TDC电路的转换速度也在纳秒级,使该电路适用于实时数据采集及高速数据处理系统。精度可调也是该设计一大特点,移位脉冲的工作频率决定了该转换系统的转换精度,通过时钟管理单元可以产生不同频率的移位时钟,从而测量精度可以根据具体需要进行适当调整。

3结束语

本基于 FPGA的时间数字转换电路设计在占用较少芯片资源的前提下,实现了很高的测量精度,工作时数据转换速度也在纳秒级;本设计电路接口简单可作为独立的功能电路使用,亦可作为功能模块 IP核[8]方便地嵌入到其他系统实现特定功能。基于 Altera芯片的时序仿真和硬件测试表明了该方法的可行性和准确性。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)