基于FPGA的级联H桥多电平变流器CPS-PWM触发脉冲快速生成

冲生成模块,两模块之间采用光纤通讯模式,具体阐述如下:

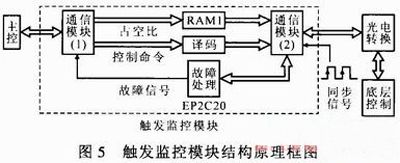

(1)顶层触发监控模块 触发监控模块主要负责触发脉冲占空比、同步信号、控制命令、底层控制参数等信息的下发;采集处理底层控制系统的功率单元运行状态以及逻辑综合、故障处理等任务,控制结构原理如图5所示。

通信模块(2)是整个触发监控系统中的关键性环节,主要承担的任务有:①接收模块(1)的译码控制命令,判断命令类型;②同步信号的编码、下发;③接收底层控制系统上传的各功率单元运行状态信息,存储到RAM2相应存储单元中并传输到故障处理模块;接收故障模块向底层控制系统发出的故障处理命令。

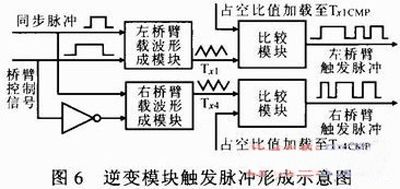

(2)底层脉冲生成模块 底层脉冲生成模块除负责脉冲生成、驱动控制任务外,还担负着整个功率单元的通信和故障处理任务。该模块主要由脉冲生成单元、通信单元及IPM驱动接口电路等几部分组成。脉冲形成单元负责CPS-SPWM触发脉冲的生成任务。脉冲生成的原理在前文中已经作了详细的介绍,这里将重点介绍各功率单元的底层控制系统脉冲生成的过程,如图6所示。

脉冲形成单元主要由载波形成模块和比较模块两大部分组成:载波形成模块用来形成三角载波。比较模块的主要任务是生成IGBT触发脉冲。即将存放在Tx1CMP/Tx4CMP中的占空比数据与Tx1/TX4中的载波数据进行比较,输出PWM触发脉冲。需要说明的是,Tx1CMP/Tx4CMP中的数据在对Tx1/Tx4进行清零或重载的同时,进行数据更新(重载)。

5 实验

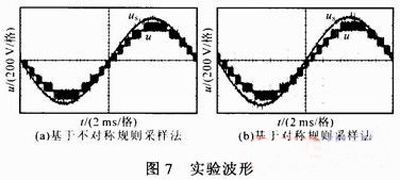

实验模型参照图1,直流侧电压Udc=90 V,载波频率1/Tc=1.28 kHz,采样周期Ts=78.125μs。脉冲传输采用编码方式,传输延时Ttr≈5μs。实验波形如图7所示。

图7a,b分别为基于对称和不对称规则采样法的输出电压u及调制波us的波形。可见,基于对称规则采样法的u滞后us约5 ms;而基于不对称规则采样法的u滞后us约3 ms,具有较快的生成速度。

6 结论

理论分析和实验结果表明:此处所述基于不对称规则采样法的CPS-SPWM脉冲生成方法,相对基于对称规则采样法的CPS-SPWM脉冲生成方法,既没有增加采样频率,也没有增加计算工作量,具有较快的生成速度。此外,由于采用了基于FPGA的CPS-SPWM脉冲生成的实现方法,为上述CPS-SPWM脉冲的快速生成提供了重要保障。

脉冲形成 CPS-SPWM技术 FPGA 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)