FPGA最小系统之:实例1 在Altera的FPGA开发板上运行第一个FPGA程序

2.5.1 实例的内容及目标

1.实例的主要内容

本节旨在通过给定的工程实例——“蜂鸣器播放梁祝音乐”来熟悉Altera Quartus II软件的基本操作、设计、编译及仿真流程。同时使用基于Altera FPGA的开发板将该实例进行下载验证,完成工程设计的硬件实现,熟悉Altera FPGA开发板的使用及配置方式。

在本节中,将主要讲解下面一些知识点。

- Quartus II工程创建及属性设置。

- Quartus II源文件设计输入方式。

- Quartus II约束设计。

- Quartus II工程编译。

- Quartus II功能仿真。

- Quartus II时序仿真。

- Quartus II硬件下载。

通过这些知识点,按照下面提供的训练流程,读者可以迅速地掌握使用Quartus II软件进行FPGA开发的方法。

2.实例目标

通过详细的流程讲解,读者应达到下面的目标。

- 熟悉Quartus II软件的操作环境。

- 熟悉Quartus II软件开发FPGA的基本流程。

- 可独立使用Quartus II软件开发新工程。

2.5.2 平台简介

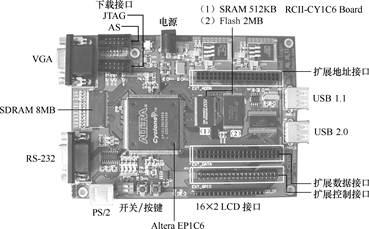

本实例基于红色飓风II代Altera板,在此开发板上集成了Altera的Cyclone一代FPGA及相关的丰富外设资源。

此开发板更加详细的信息、扩展附件及使用方法,可以到红色飓风的官方网站:http://www.fpgadev.com获取更多的信息。

本实例将在这个开发板上对Altera的FPGA设计流程做一个全面的介绍,依照此例程的流程便可在该开发板上运行一个FPGA程序。如图2.29所示为此开发板的外观图。

图2.29 红色飓风II代Altera板外观图

2.5.3 实例详解

本节将使用图解的方式将整个流程一步一步展现给读者,使读者能够轻松掌握Quartus II的开发流程。

1.工程创建及属性设置

(1)启动Quartus II软件。

安装Quartus II软件后,在桌面或者程序组中启动Quartus II软件。

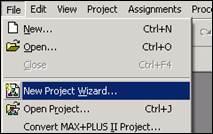

(2)打开新工程向导。

启动软件后,选择“File”菜单的“New Project Wizard”选项,打开新建工程向导,如图2.30所示。在新建工程向导的 “介绍”页面中,单击“Next”按钮进入下一页。

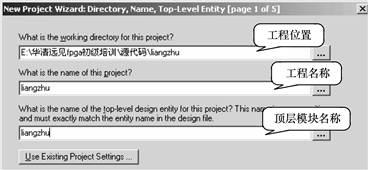

(3)设置工程属性。

如图2.31所示,在新建工程向导的第一页对工程工作目录、工程名称以及顶层模块名称进行设置。

图2.30 新建工程

图2.31 设置工程属性

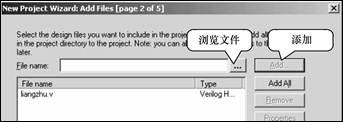

(4)添加设计文件。

在新建工程向导的第二页选择为工程添加设计文件,如图2.32所示。

图2.32 添加设计文件

(5)选择FPGA器件。

在新建工程向导的第三页,为工程配置相应的器件型号和参数,如图2.33所示。选取的器件型号将在完全编译时将工程设计映射到对应的器件逻辑资源上。

图2.33 选择器件型号

(6)完成工程创建。

配置完器件属性后,选择Quartus II默认的综合工具、仿真工具及时序分析工具,完成工程的创建。

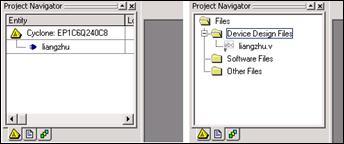

选择软件左侧的工程浏览器的 按钮来管理已添加的文件。如图2.34所示,左边为工程层次窗口,右边为设计文件窗口。

按钮来管理已添加的文件。如图2.34所示,左边为工程层次窗口,右边为设计文件窗口。

图2.34 工程结构窗口

2.设计输入

(1)添加设计文件。

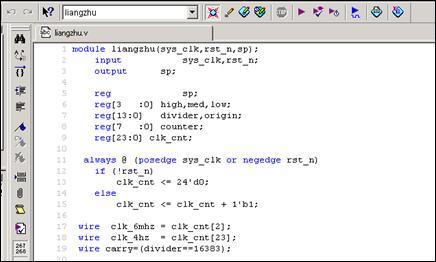

如果在创建工程时没有为工程添加设计文件,可以选择“Project”菜单的“Add/Remove Files in Project”选项,为工程添加设计文件。在本实例中,读者可向工程添加实例代码中的liangzhu.v文件。

添加后,在工程浏览器中双击liangzhu.v图标,即可查看该Verilog设计文件,如图2.35所示。

图2.35 Verilog设计文件

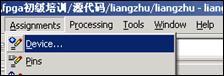

(2)配置器件属性。

同样的,如果在创建工程时没有为工程配置器件型号及属性,可以在工程浏览器的工程实体图标上单击右键,选择“Device”选项,为工程配置器件属性,如图2.36所示。

若在建立工程时已经配置好,则可单击“Device Pin Options…”按钮,进一步设置器件的相关属性,如图2.37所示。

图2.36 器件选择 图2.37 器件属性配置

在如图2.38所示的对话框中,可对FPGA所使用的配置芯片及未用管脚等进行配置。

图2.38 指定配置模式

选择“Unused Pins”选项卡,将不使用的管脚配置为三态,如图2.39所示。

图2.39 未用管脚置三态

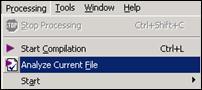

(3)分析工程。

编写设计输入文件后,首先要进行工程分析,目的是为了检查设计输入的语法。单击 “Start Analysis Synthesis”按钮分析工程,如图2.40所示。

“Start Analysis Synthesis”按钮分析工程,如图2.40所示。

图2.40 分析工程选项

查看信息栏,修改所有出现的错误,直到分析通过,如图2.41所示。

图2.41 分析工程结果,没有报错

3.约束设计

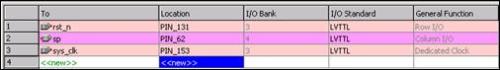

(1)管脚分配。

管脚分配的作用在于将设计输入文件的端口与实际的器件进行映射,实现设计输入模块端口在实际器件管脚上的实例化。在Quartus II软件中可以在管脚分配主窗口中对管脚的分配进行设置,如图2.42所示。

图2.42 管脚分配

通过工具栏中的快捷按钮可以帮助用户快速的进行管脚分

Cyclone Altera FPGA QuartusII FPGA最小系统 相关文章:

- FPGA最小系统之:最小系统电路分析(06-05)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 有功电能计量IP核的设计(06-05)

- 14nm的FPGA需要什么样的电源管理IC?(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:设计需求分析与功能定义(06-04)

- 如何提高图像处理的实例分析(12-20)