FPGA最小系统之:最小系统电路分析

2.2.1 FPGA管脚设计

FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。

下面以Altera公司的Cyclone系列FPGA为例,介绍FPGA的各种功能管脚。

(1)用户I/O。

I/Onum(LVDSnumn):可用作输入或输出,或者双向口,同时可作为LVDS差分对的负端。其中num表示管脚序号。

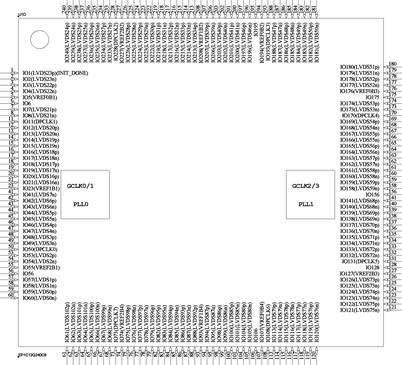

一般在绘制FPGA原理图时,将同一种功能和用途的管脚放在一个框图中,如图2.3所示是用户I/O的原理图。

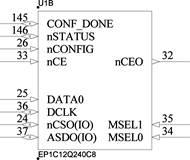

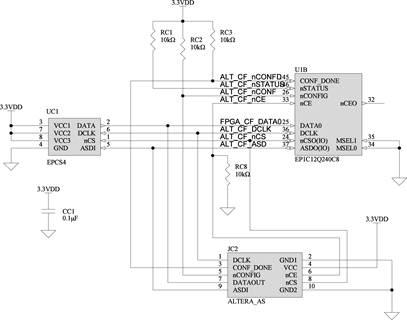

(2)配置管脚。

- MSEL[1..0]:用于选择配置模式。FPGA有多种配置模式,比如主动、被动、快速、正常、串行、并行等,可以此管脚进行选择。

- DATA0:FPGA串行数据输入,连接至配置器件的串行数据输出管脚。

- DCLK:FPGA串行时钟输出,为配置器件提供串行时钟。

- nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚。

- ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚。

- nCEO:下载链器件使能输出。在一条下载链(Chain)中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应悬空。

图2.3 FPGA用户I/O原理图

- nCE:下载链器件使能输入,连接至上一个器件的nCEO。下载链第一个器件的nCE接地。

- nCONFIG:用户模式配置起始信号。

- nSTATUS:配置状态信号。

- CONF_DONE:配置结束信号。

如图2.4所示是FPGA配置管脚原理图。

图2.4 FPGA配置管脚原理图

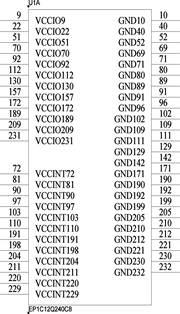

(3)电源管脚。

- VCCINT:内核电压。通常与FPGA芯片所采用的工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V。

- VCCIO:端口电压。一般为3.3V,还可以支持选择多种电压,如5V、1.8V、1.5V等。

- VREF:参考电压。

- GND:信号地。

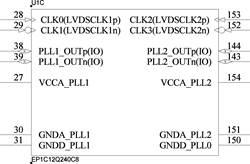

(4)时钟管脚。

- VCC_PLL:锁相环管脚电压,直接连VCCIO。

- VCCA_PLL:锁相环模拟电压,一般通过滤波器接到VCCINT上。

- GNDA_PLL:锁相环模拟地。

- GNDD_PLL:锁相环数字地。

- CLKnum(LVDSCLKnump):锁相环时钟输入。支持LVDS时钟输入,p接正端,num表示PLL序号。

- CLKnum(LVDSCLKnumn):锁相环时钟输入。支持LVDS时钟输入,n接负端,num表示PLL序号。

- PLLnum_OUTp(I/O):锁相环时钟输出。支持LVDS时钟输入,p接正端,num表示PLL序号。

- PLLnum_OUTn(I/O):锁相环时钟输出。支持LVDS时钟输入,n接负端,num表示PLL序号。

如图2.6所示是FPGA时钟管脚原理图。

图2.5 FPGA电源管脚原理图 图2.6 FPGA时钟管脚原理图

另外,FPGA的管脚中,有一些是全局时钟,这些管脚在FPGA中已经做好了时钟树。使用这些管脚作为关键时钟或信号的布线可以获得最佳性能。

(5)特殊管脚。

- VCCPD:用于选择驱动电压。

- VCCSEL:用于控制配置管脚和锁相环相关的输入缓冲电压。

- PORSEL:上电复位选项。

- NIOPULLUP:用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

- TEMPDIODEn/p:用于关联温度敏感二极管。

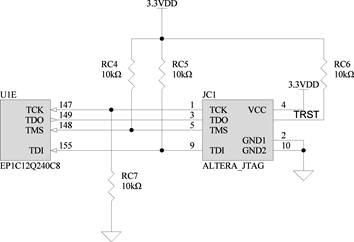

2.2.2 下载配置与调试接口电路设计

FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)两种。其中EPCx系列为老款配置芯片,体积较大,价格高。而EPCSx系列芯片与之相比,体积小、价格低。

另外,除了使用Altera公司的配置芯片,也可以使用Flash+CPLD的方式去配置FPGA。

在把程序固化到配置芯片之前,一般先使用JTAG模式去调试程序,也就是把程序下载到FPGA芯片上运行。虽然这种方式在断电以后程序会丢失,但是充分利用了FPGA的无限擦写性。

所以一般FPGA有两个下载接口:JTAG调试接口和AS(或PS)模式下载接口。所不同的是前者下载至FPGA,后者是编程配置芯片(如EPCSx),然后再配置FPGA。

如图2.7和图2.8所示分别是JTAG模式和AS模式的电路原理图。

图2.7 JTAG模式原理图

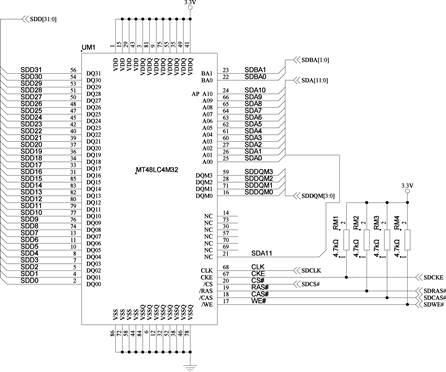

2.2.3 高速SDRAM存储器接口电路设计

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。

一般比较常用的SDRAM包括现代HY57V系列、三星K4S系列和美光MT48LC系列。例如,4M×32位的SDRAM,现代公司的芯片型号为HY57V283220,三星公司的为K4S283232,美光公司的为MT48LC4M32。这几个型号的芯片可以相互替换。SDRAM典型电路如图2.9所示。

图2.8 AS模式原理图

图2.9 SDRAM典型电路

2.2.4 异步SRAM(ASRAM)存储器接口电路设计

由于ASRAM的读写时序相对比较简单,因此一般使用SRAM作为数据的

Cyclone Altera Flash FPGA CPLD SDRAM FPGA最小系统 相关文章:

- FPGA最小系统之:实例1 在Altera的FPGA开发板上运行第一个FPGA程序(06-05)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 有功电能计量IP核的设计(06-05)

- 14nm的FPGA需要什么样的电源管理IC?(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:设计需求分析与功能定义(06-04)

- 如何提高图像处理的实例分析(12-20)