FPGA最小系统之:实例1 在Altera的FPGA开发板上运行第一个FPGA程序

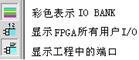

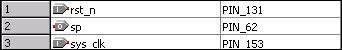

配,如图2.43所示。

通过管脚分配主窗口中的管脚信息可以看到管脚的I/O种类、管脚的序号、Bank所在的位置、I/O使用的电压标准等,如图2.44所示。

图2.43 指定管脚快捷按钮 图2.44 管脚信息

(2)其他约束。

除了对工程的管脚进行约束外,Quartus II软件还允许用户对其他的一些约束进行设置,例如面积约束、速度约束、时钟约束、资源约束等。这些约束都属于较为严格的工程设置,在本实战训练中无需考虑。

4.编译工程

(1)完全编译。

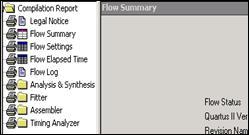

有了完整的设计输入、完整的约束条件后,就可以对工程进行完全编译了,如图2.45所示是完全编译的选项。

根据工程复杂度的不同,Quartus II在进行完全编译时所消耗的时间差异也很大。在工程浏览器中显示了编译的类别及进度,帮助用户了解编译的进程。

图2.45 完全编译选项 图2.46 编译状态

若在编译过程中出现错误提示,用户可在信息栏中查看错误的信息,修改所有存在的错误后重新进行编译,直到能够无错误地完成编译,如图2.47所示。

图2.47 编译结果信息栏

(2)编译报告。

Quartus II编译结束后,为用户提供了一个完整而详细的编译报告。通过该报告,用户可以查看工程使用资源的情况及系统可以达到的性能,如图2.48所示。

5.功能仿真

(1)建立仿真文件。

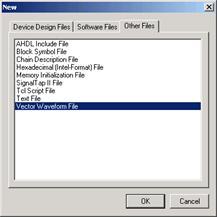

选择Quartus II软件“File”菜单的“New”选项,打开新建其他文件对话框,选择新建波形图文件,如图2.49所示。

图2.48 编译结果报告 图2.49 新建波形图

(2)添加观察信号。

用户可以通过双击波形窗口中的空白区域为工程添加需要观察的信号,如图2.50所示。

图2.50 仿真波形窗口

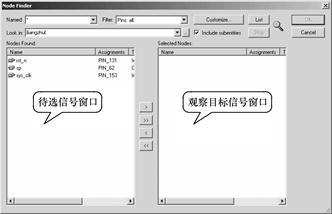

在打开的插入节点或总线对话框中,打开“Node Finder…”(节点查找器),如图2.51所示。通过节点查找器,用户可以方便地选择需要观察的信号。

图2.51 插入节点或总线对话框

选择Filter:“Pins:all”,然后点击list列出所用输入/输出端口,如图2.52所示。

图2.52 节点查找器

选中所有信号,单击 按钮,即可将选中信号加入观察目标窗口中,如图2.53所示。

按钮,即可将选中信号加入观察目标窗口中,如图2.53所示。

图2.53 已添加好的信号

(3)设置仿真时间最小间隔。

考虑到硬件环境提供的是50MHz的时钟,即时钟周期为20ns,设置“Grid Size”为20ns。选择“Edit”菜单的“Grid Size”选项进行设置,如图2.54所示。

(4)设置仿真时间长度。

选择“Edit”菜单的“End Time”选项,设置仿真时间长度为10ms,如图2.55所示。

(5)添加激励信号。

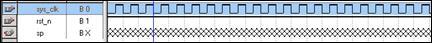

选中sys_clk信号,单击 时钟按钮,将该信号设置为时钟波形,周期为20ns,如图2.56所示。此信号代表了系统时钟。

时钟按钮,将该信号设置为时钟波形,周期为20ns,如图2.56所示。此信号代表了系统时钟。

图2.55 设置仿真结束时间 图2.56 设置时钟

选中rst_n信号,单击 高电平按钮,将该信号设置为1。此信号代表了复位信号。

高电平按钮,将该信号设置为1。此信号代表了复位信号。

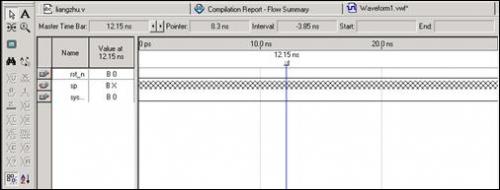

添加激励信号后,选择保存文件,此时的波形如图2.57所示。

图2.57 以设置好的输入波形

(6)生成功能仿真网表。

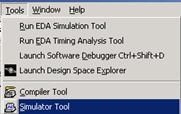

选择“Tools”菜单的“Simulator Tool”选项,打开仿真器,如图2.58所示。

将仿真器的仿真模式设置为“Functional”(功能仿真),如图2.59所示。

图2.58 仿真器选项 图2.59 仿真对话框

单击“Generate Functional Simulation Netlist”按钮产生仿真网表。仿真网表是将工程设计文件进行编译及映射后生成的用于进行仿真的文件,仿真器根据仿真网表进行仿真,直接反应了工程设计文件的真实情况。

(7)开始功能仿真。

单击“Start”按钮开始进行功能仿真,如图2.60所示,可以看到仿真的进度,根据工程的复杂度,仿真过程所消耗的时间也有所不同。

图2.60 仿真进度

仿真完成后单击“open”按钮打开仿真结果,如图2.61所示。

图2.61 仿真波形结果

6.时序仿真

功能仿真后,如果波形没有问题,开始做时序仿真,检查波形延时对设计是否有影响。

选择“Tools”菜单的“Simulator Tool”选项,打开仿真器,选择仿真模式为“Timing”,即时序仿真模式,如图2.62所示。

图2.62 选择时序仿真

单击“Start”按钮,开始时序仿真。时序仿真比功能仿真要慢一些。

仿真完成后,查看仿真结果。通过波形可以看到产生了7.06ns的延时,如图2.63所示。

图2.63 查看仿真结果

可以看到,功能仿真并不包含延迟,而时序仿真则会根据具体的器件参数配置及资源使用情况将延迟仿真出来。功能仿真主要用于验证工程设计文件逻辑的正确性,而时序仿真更能体现真实的硬件运行过程中设计文件的执行过程。

7.下载程序

仿真验证结束后,用户就

Cyclone Altera FPGA QuartusII FPGA最小系统 相关文章:

- FPGA最小系统之:最小系统电路分析(06-05)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 有功电能计量IP核的设计(06-05)

- 14nm的FPGA需要什么样的电源管理IC?(06-04)

- 高速PCI信号采集卡设计与实现综合实例之:设计需求分析与功能定义(06-04)

- 如何提高图像处理的实例分析(12-20)