FPGA与DSP协同处理系统设计之: FPGA与DSP的通信接口设计

次读写必须执行成对的16位操作。

对于C64xx系列DSP,HPI可以选择16位(HPI16)和32位(HPI32)两种模式。

对于C621x、C671x系列DSP,HPI口内部有3个寄存器,分别是控制寄存器(HPIC)、地址寄存器(HPIA)和数据寄存器(HPID)。这3个寄存器可以直接被主机访问,主机每执行一次对CPU内部存储空间的访问都必须先对控制寄存器和地址寄存器写入相应的值,然后才能对数据寄存器进行读写操作。

HPI口的外部接口是由数据总线HD[15:0]以及一部分用于描述和控制HPI接口的控制信号组成,这些控制信号的具体类型如表11.4所示。

表11.4 HPI信号描述

引脚 | 描述 |

HCNTL[1:0] | 控制HPI的操作类型 |

HHCNTL | 半字确认输入,“0”、“1”分别表示一次字传输的第一个半字和第二个半字 |

HR/W | 读/写选择 |

续表

引脚 | 描述 |

HRDY | 就绪状态标志 |

HINT | 中断标志,DSP向主机提出中断 |

HAS | 区别地址/数据复用总线的数据与地址 |

HDS1、HDS2、HCS | 数据选通输入,三者配合可用于产生一个HPI内部选通信号HSTROBE,这个信号可以用以下公式来描述: HSTROBE=[NOT(HDS1XORHDS2)]ORHCS |

对于一个写HPI口的操作,应首先使能HCS,变化HDS1或HDS2,可使HSTROBE信号产生一个下降沿。HPI口在这个下降沿采样控制信号HCNTL[1:0]、HHWIL和HR/W,同时在使能HCS的同时驱动HRDY,以使主机进入等待状态。直到HRDY产生下降沿,表明HPID已清空,可以接收新的数据。此时HSTROBE也将产生一个上升沿,并采样HD[15:0]上的数据并将其送入HPID,以完成第一个半字的写入。

对于第二个半字的写入,由于32位的HPID已经清空,可以直接写入数据。不会出现未准备好的情况,所以HRDY一直保持为低,与第一个字节的写入相同。该操作也在HSTROBE的下降沿采样控制信号,并在HSTROBE的上升沿采样数据总线HD[15:0]的数据并送HPID,以完成一个32位的写入操作。

2.FPGA与DSP的HPI连接实例

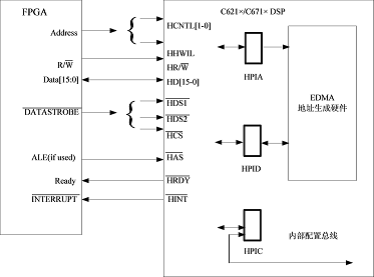

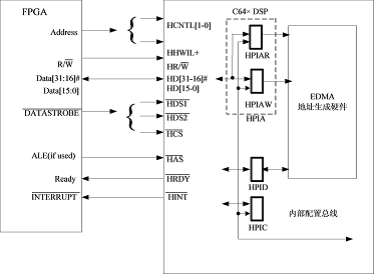

FPGA与HPI的接口连接比较简单,就是将HPI接口相关的信号全部连接到FPGA的管脚。如图11.8和图11.9所示分别是FPGA和TI不同系列的DSP的连接框图。

图11.8FPGA与C621x、C671x系列DSP的HPI接口互联框图

图11.9FPGA与C64x系列DSP的HPI接口互联框图

DSP 协同处理 FPGA 通信接口 EMIF HPI BlockRAM 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)