FPGA与DSP协同处理系统设计之: FPGA与DSP的通信接口设计

模块。

这些模块都是完全同步、真正的双端存储器。用户可独立地从每个端口读出或向每个端口写入(但同一地址不能同时进行读和写)。另外,每个端口都有一个独立的时钟,并且对每个端口的数据宽度都可以独立进行配置。如图11.6所示为双端RAM模块的框图。

由FPGA逻辑和一批BlockRAM组成的FIFO取决于所构建的FIFO要求的宽度和深度。FIFO可使用XilinxCOREGenerator™工具构建,或者可以用HDL手动组合。

使用COREGenerator工具构建FIFO具有一定优势,即设计可以达到并实现很高的性能指标。按照设计规范用HDL构建的设计则可赋予设计人员完全的设计自由。

3.FPGA与DSP的EMIF连接

FPGA的灵活性使我们可以将其用做具备可选择总线宽度(8位~64位)的各类存储器而创建不同的设计。通过接口设计,可将FPGA用做同步或异步标准存储器,或同步或异步FIFO。通过接口设计,可将FPGA以同步或异步的方式连接到EMIF。

在同步模式中,ECLKOUTx时钟用于驱动FPGA接口逻辑。此时钟甚至可以驱动整个FPGA。FPGA的逻辑功能、专用乘法器、PPC405或MicroBlaze™处理器等使其具备了强大的处理功能。这样,FPGA就可以用做协处理器或高速数据处理和传输器件。

FPGA的存储器容量小于TMSC64x类型DSP的寻址空间。FPGA存储器必须使用FPGABlockRAM来实现。上述TMSC64x到FPGA的接口为FIFO结构,可以使用BlackRAM资源来实现。

FIFO接口可使用标准的TMSC64xEMIFFIFO接口机制。如表11.3所示为EMIF信号的总结。

表11.3 EMIF与FPGA的接口信号

信号名称 | 方向 |

CE | DSP输出 |

AOE | DSP输出 |

AWE | DSP输出 |

ARE | DSP输出 |

INTx | DSP输入 |

INTy | DSP输入 |

INTz | DSP输入 |

ED[63:0] | DSP双向 |

FIFO要求连续地读时钟和连续地写时钟。这些时钟由ARE和AWE信号生成,使用FPGA的本地时钟控制功能进行布线。

DSP具有3.3V的接口逻辑,所以用于连接到EMIF的I/O组(bank)必须指定为3.3VVCCIO。如果无法指定,就必须使用电平移位器件。这一器件可为两个器件间的信号通路引入额外的时间。

4.FIFO接口的设计实例

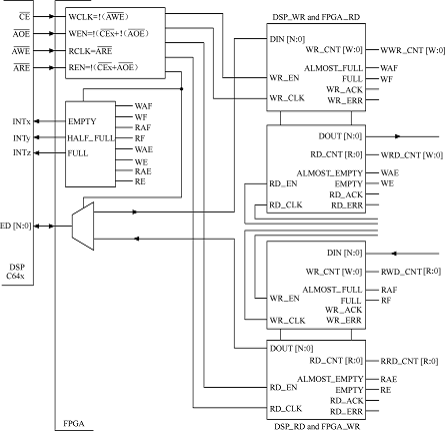

本设计使用了标准的EMIFFIFO设置。如图11.7所示为用于Xilinx公司的Virtex-IIPro和Spartan-3器件的设计示例。

图11.7基于FIFO的EMIF接口实例

数据组芯片使能信号(Cex)与异步输出使能(AOE)一起,用于为设计的写或读FIFO部分生成使能信号。此信号还用于为数据多路复用器和标志选择逻辑生成使能信号。

FIFO的读写时钟通过本地时钟布线直接布线到FIFO时钟输入。

FIFO中使用的RAMB16组件由于沿着与EMIF相连接的I/O块进行排列,显著改善了时序。当BlockRAM组件的列的大小与使用的I/O的数量相同时,即可构建快速的矩形接口。

本设计使用常规的FIFO标志输出。要对标志逻辑施加额外控制,无论是针对DSP端还是FPGA端,可使用写计数器和读计数器输出。

信号AINIT(图11.7中未显示)强制所有标志为高有效状态。AINIT发出后,在第一个WR_CLK上,FULL和ALMOST_FULL标志变为无效,呈低状态。对于在首个RD_CLK边沿上的EMPTY和ALMOST_EMPTY标记,也会发生同样情况。

ALMOST_EMPTY和ALMOST_FULL标志表明只剩下了一个FIFO位置。使用WR_COUNT和RD_COUNT输出,可以构建用户定义的FIFO标志。这两个计数器的值都不反映FIFO内容(地址)的准确位置。FIFO的两个端口(时钟域)都存在时钟延迟,长度为一个时钟周期。

输出WR_COUNT和RD_COUNT为被延迟的内部FIFO高位地址计数器。为输出选择两个比特,即可将FIFO的位置确定到总尺寸的四分之一(如下面计数器解码示例中所示)。

计数器越宽,位置就能越精细。下面是计数器解码示例。

·COUNT[1:0]=0b00表明FIFO小于1/4满或1/4空。

·COUNT[1:0]=0b01表明FIFO在1/4和1/2满之间或1/4和1/2空之间。

·COUNT[1:0]=0b10表明FIFO在1/2和3/4满之间或1/2和3/4空之间。

·COUNT[1:0]=0b11表明FIFO大于3/4满或3/4空。

DSP对不同标志的反应取决于FPGA中读写FIFO的状态。

11.3.2基于TMS320系列DSP的主机接口(HPI)设计

1.HPI接口简介

HPI接口是一种数据宽度为16位的并行端口(C64xx系列DSP中,HPI口的数据宽度达到32位)。通过HPI口,主机可以直接对CPU的存储器空间进行操作。

在C621x、C671x系列DSP中,没有留出专门的EDMA通道来执行HPI口的访问操作,而是直接将HPI口连接到内部的地址产生硬件上,因而提高了对内部存储空间的访问速度。

HPI口内部加入了两个8级深度的读写缓冲,可以执行地址自增的读写操作,提高读写操作的吞吐量。HPI口为内部CPU提供了标准32位的数据接口,同时为外部主机也提供了一个经济的16位接口,所以对外部主机而言,每

DSP 协同处理 FPGA 通信接口 EMIF HPI BlockRAM 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)