基于FPGA的数字分频器设计

计一个分频系数为3.6的分频器,将小数部分的6按倍累加,假设累加的值为a,如果a<10,则进行3分频,如果a<10下一次则加上6。此后,如果a>=10,则进行4分频,4分频过后再将累加值减去4后与10比较以决定下一次分频是4分频还是3分频,这样分频器设计成6次4分频,4次3分频,总的分频值为(6×4+4×3)/(6+4) = 3.6。

2.3 分数分频器的设计

分数分频器的数据输入部分与小数分频基本相同,差别仅在于数码管显示部分显示三位分频系数。由于分数在一定情况下可以转化为小数进行计算,所以分数分频的设计思想与小数分频的很相似。假设进行分频,总分频数由分母m决定,规律是进行n次j+1分频和m-n次j分频。两种分频交替进行的计算方法和小数分频的很类似。累加分结果是大于等于分母还是小于分母决定是进行j分频还是j+1分频。

3. 数字分频器的FPGA设计及仿真

利用FPGA对8192kHz的基准时钟进行时钟分频,分别得到1024kHz、512kHz、256kHz和1kHz的时钟频率,需要分别进行8分频、16分频、32分频和8192分频。在利用FPGA进行设计整数分频器时,通过VHDL硬件描述语言利用计数器方式来实现。

3.1 1024kHz时钟分频

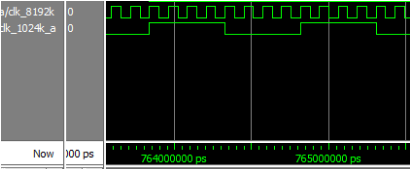

根据所需的时钟频率为1024kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是8倍的整数倍关系,因此需要对8192kHz的晶振时钟进行8分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行8分频的分频器设计。然而8又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-1所示。

图3-1 1024kHz时钟分频

由图3-1得知,当8192kHz的晶振时钟输入8个时钟,系统输出1个时钟,即一个1024kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-3时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。

3.2 512kHz时钟分频

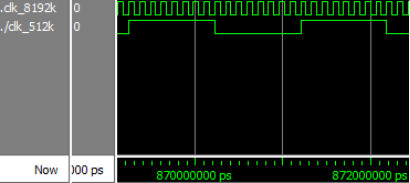

根据所需的时钟频率为512kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是16倍的整数倍关系,因此需要对8192kHz的晶振时钟进行16分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行16分频的分频器设计。然而16又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-2所示。

图3-2 512kHz时钟分频

由图3-2得知,当8192kHz的晶振时钟输入16个时钟,系统输出1个时钟,即一个512kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-7时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。

3.3 256kHz时钟分频

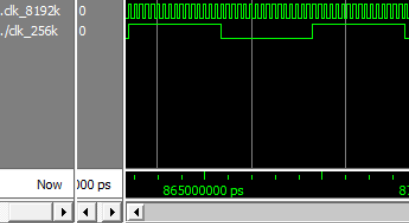

根据所需的时钟频率为256kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是32倍的整数倍关系,因此需要对8192kHz的晶振时钟进行32分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行32分频的分频器设计。然而32又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-3所示。

图3-3 256kHz时钟分频

由图3-3得知,当8192kHz的晶振时钟输入32个时钟,系统输出1个时钟,即一个256kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-15时,输出时钟信号进行翻转,同时给计数器一个复位信号,使下一个时钟上升沿到来时,计数器重新开始计数,不断循环下去。

3.4 1kHz时钟分频

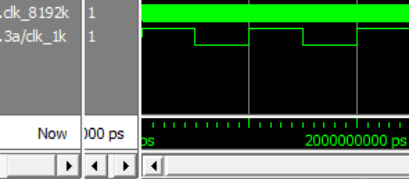

根据所需的时钟频率为1kHz的时钟,而晶振时钟的频率为8192kHz,晶振时钟与所需的时钟频率恰巧是8192倍的整数倍关系,因此需要对8192kHz的晶振时钟进行8192分频来获得所需要的时钟。根据整数倍分频器的设计方法原理,通过ISE9.1逻辑设计工具,利用VHDL硬件描述语言来进行8192分频的分频器设计。然而8192又是偶数,所以需要设计的是偶数分频器。对设计的内容通过Modelsim6.5仿真软件进行仿真验证,结果如图3-4所示。

图3-4 1kHz时钟分频

由图3-4得知,当8192kHz的晶振时钟输入8个时钟,系统输出1个时钟,即一个1kHz频率的时钟。程序设计中采用计数器来实现,当计数器值为0-((n/2)-1)=-4095时,输出时钟信号进

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)