基于FPGA的扫频信号源的研究与设计

在研究过程中,取相位累加器的输出位数是32位,而对于“一次多位”的加法器来讲,最长的延迟来自进位的脉冲通过所有阶段的时候。目前已经采取了许多技术来缩短这一进位延迟,由于在老一代FPGA中没有提供内部快速进位逻辑,可以通过跳跃进位、先行进位和进位选择加法器来提高加法运算的速度,但是在现代FPGA系列中都具有特别快的“脉冲进位逻辑”,所以本设计采用进位流水线技术,这样不但提高了累加器的运算速度,而且降低了设计复杂度。流水线技术是将一个算术操作分解成一些基本操作以达到提高工作速度的一种技术,因此流水线加法器可以作为提高加法器速度的首眩本设计将32位累加器分成4条流水线,每条流水线完成8位的加法运算,流水线的进位进行级联。采用流水线结构可以提高器件的运算速度。

由于频率控制字只在频率控制字更新后的前4个周期变化,以后各个周期不再变化。基于这种情况,可以对累加器进行改进,从而节省部分存储器。改进的流水线的结构图及在FPGA中综合结果如图2所示。

当频率控制字开始变化时,DDS控制器发送控制信号Start,开始输出控制信号,第一个时钟上升沿到来,将clk1置高,频率控制字FSW的低8位写入第一级流水线的寄存器,第二个时钟上升沿到来,写入FSW的次低8位,以此类推,第四个时钟周期上升沿到来,完成数据输入。在以后的周期内,这些数据将保持不变,直至下一次数据刷新。所以,此流水线设计不仅提高了速度,而且相对减少了寄存器的数量。在EP2C20中实现累加器,采用流水线累加器与传统的累加器速度和资源比较如表1所示。

仿真结果表明,采用进位级联的流水线技术,既能保证较高的资源利用率,又大幅度提高了系统性能和速度。

2.3 ROM压缩算法

在设计中为节省ROM的空间,尽量节省芯片资源,通常累加器的寄存器输出只有其高K位被用于频率合成,其余的较低的N-K位则舍弃不用,这就是所谓的相位截断。在实际应用中,还希望进一步节约ROM的占用,而ROM压缩最简单的方法是利用正弦信号的对称性,利用一个象限的信号通过地址变换来表示全部的正弦信号。

sin(x)函数在0~2π区间内,它是关于x=π的奇函数。即:

所以只需将0~2π区间的相位编码减去π,求出其幅度值后在加移负号,这样的效果就相当于直接对π~2π区间相位求sin值。这个负号要以数字编码的形式表现出来,所以,π~2π区间的幅度序列是0~π区间幅度序列的补码。在0~π区间,sin(x)函数是关于x=π/2的偶函数。所以:

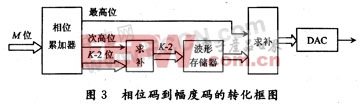

可见,当相位处于π/2~π区间时,将此时的相位编码减去π/2后,在以π/2为模对其求补,这样得到的相位值就是处于0~π/2区间并和原相位值有相同的函数值,在以这个相位码对ROM寻址,得出的幅度就是π/2~π区间对应幅值序列。即ROM中只存储0~π/2的幅度序列,然后通过相位求补,获得0~π的幅度码,通过幅度求补获得π~2π的幅度码。优化后的相位码到幅度码的转化框图如图3所示。

这样就完成了整个波形的拼接,实现用ROM只存储1/4周期波形而可以输出整个周期,减少了ROM的2位地址,ROM表压缩比达到了4:1,且硬件电路比较容易实现。

3 信号调理电路

信号调理电路包括低通滤波器和功率放大2部分。

经过D/A转化输出信号含有高频噪声,故要对其进行滤波处理,滤除不需要的频率分量,以便输出频谱纯净的正弦信号。本系统选用7级椭圆低通滤波器,其截止频率为9.8 MHz。功率放大部分是为了提高扫频信号源驱动后级负载的能力。该放大电路选用高速宽带运放MAX 4117及三极管2N2905,2N2219,其带宽可达到300 Mb/s,输入输出阻抗均为50 Ω。

4系统性能及测试结果

本系统采用Altera公司的EP2C20F484C8为主控制器,D/A转换器选用AD公司的AD9761,AD9761是一个双通道,具有40 MSPS的精度为10位的高速CMOS DAC,并内置2倍数插值FIR滤波器。

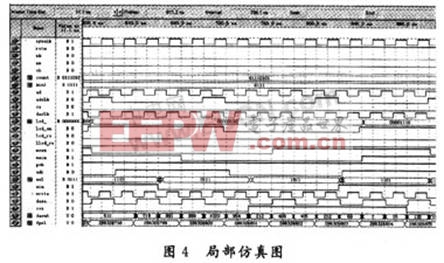

在QuartusⅡ中进行时序仿真,系统的局部仿真结果如图4所示。

通过QuartusⅡ中的嵌入式逻辑分析仪SignalTapⅡ分析结果如图5所示。

测试结果表明,本系统设计的扫频信号源在线性扫频模式下,完全达到了预期的设计目的。

系统最终在硬件电路中测试结果如下:最大扫频范围:DC~10 MHz,扫频宽度可在此范围内任意设定;最小扫频步长:50 Hz;扫频速度:100 Hz/s;输出波形幅值范围:0~5 V;幅值分辨率:50 mV。

5 结语

本扫频信号源采用DDS技术,完成对相位累加器和相位幅度转化电路的优化设计,与相比利用FPGA芯片将扫频信号源的硬件电路集成在一个片上系统,提高整个系统的工作频率,并减少了寄存器的占用数量。

所有电路模块采用Verilog HD

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)