基于AD7762和FPGA的数据采集系统设计

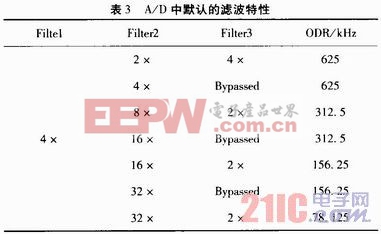

为低电平期问依次将两个寄存器的地址和内容写入A/D中,控制A/D的工作状态。 表3是在A/D内部时钟为20 MHz时,可看出当rate=3’h3时→625 kHz;rate=3→312.5 kHz;rate=4→156.25 kHz;rate=5→78.125 kHz。 A/D寄存器写成功后,A/D会根据寄存器设置的工作状态进行数据采样和传输。当一个新的转换数据结果有效时,A/D的 模块中ad_data_bus[15.0]与FPGA的IO口进行连接。ad_rst_n是A/D的复位信号,而rst_n是系统的复位信号。ad_mclk外接40 MHz晶振,进入A/D后经过寄存器设置进行二分频。ad_sync是同步信号,可以同步多片ADC,此处不操作。 对A/D进行仿真。从仿真图中可以看出,A/D产生 3.4 串口数据传输模块

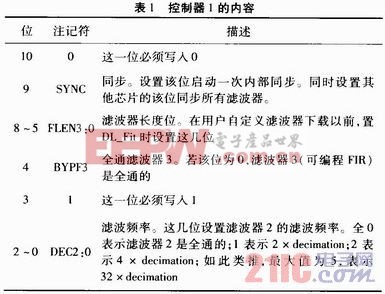

控制寄存器1的地址是0X0001,设计中控制寄存器1的内容设为0X001B。设计中通过写控制寄存器1设置输出数据频率。读时序控制A/D采样数据的输出。A/D的控制时序及工作状态如图4所示。

AD7762串联了3个滤波器。通过使用不同的滤波频率、滤波器选择和全通的结合,可以获得大范围的采样速率。通过设置寄存器1的低3位滤波器的状态设置数据输出速率Rate,A/D中默认的滤波特性如表3所示。

3.2 A/D读时序控制

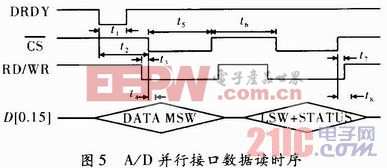

AD7762的读时序如图5所示。

引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当

引脚会产生一个低脉冲信号送给FPGA,当FPGA接收到这个低脉冲信号时开始接收A/D的采样数据。由于AD7762是24位分辨率的A/D转换器,而外部是16位数据线,所以从AD7762中读取一个转换结果,需要执行两次16 bit读数据操作。当 同时为低电平时,数据总线开始传播数据。在二次读操作之间,

同时为低电平时,数据总线开始传播数据。在二次读操作之间, 必须置高一个ICLK周期的高电平。数据传输结束后

必须置高一个ICLK周期的高电平。数据传输结束后 保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

保持高电平,数据线处于高阻态,等待下一次有效数据的传输。

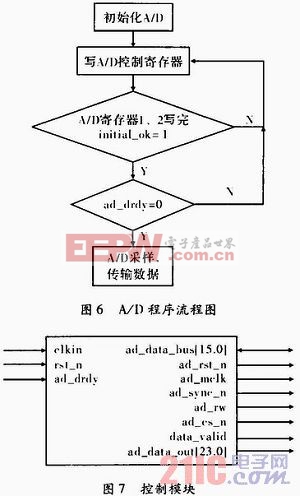

控制A/D的程序流程图如图6所示。程序编译后生成的A/D转换器的控制模块如图7所示。

将程序通过FPGA的JTAG口下载到硬件系统,进行仿真得到的A/D模块仿真结果如图8所示。

低电平后才开始根据

低电平后才开始根据 的高低电平控制传输数据。

的高低电平控制传输数据。

3.3 FIFO数据缓存模块

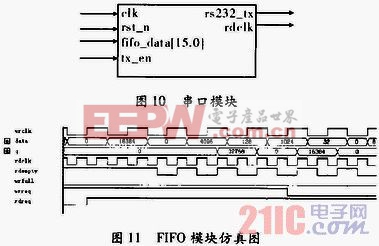

FIFO用于存储FPGA接收的A/D采集的数据,FIFO模块的读时钟受前端A/D模块巾的data_valid信号控制,写时钟由后面的串口模块产生,已达到FIFO数据读取与串口传输的数据一致。保证数据准确地通过串口传输到上位机。FIFO的读写控制信号分别由wrfull和rdempty控制,FIFO模缺如图9所示。

串口模块的开启和关闭信号tx_en受FIFO模块的读信号rdreq控制。

数据采集系统设计中,AD7762内部设置差分放大器和灵活设置的寄存器,使得外部的电路设计简单且成本低。FPGA控制更为灵活方便,若想改变A/D的工作状态只需要更改寄存器的设置内容即可。减少外部控制线的数量,使系统减小干扰,更为可靠。若将此系统作为音频信号分析系统的前端,将使整个系统的稳定度及精确度得到提高。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)