集成式比特误码率测试仪在FPGA中的应用

View by Function\DebugVerification\Chipscope Pro\下双击Ibert,如图2所示。按顺序设置Ibert核线速率2.457 6 Gbit·s-1,数据宽度20 bit,参考时钟频率122.88 MHz,选择被测试的GTP DUAL,设置系统时钟频率66 m、位置R7等参数,IBE RT Core Summary如图3所示,点击generate生成Ibert核的可下载bit配置文件。

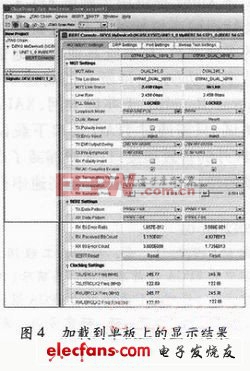

(2)将生成的bit文件加载到单板上,显示界面如图4所示。

首先关注PLL Status状态和Clocking Setting显示的收发时钟频率,PLL Status状态Locked表明GTP_DUAL的PLL已锁定GTP的参考时钟,GTP可正常工作。如状态是Unlocked,则要检测待测GTP的参考时钟是否正常输入。

测试高速串行信号的信号质量,通常使用足够带宽和采样率的示波器测试信号眼图来评估,一但测试的眼图不符合模板要求,需要调整高速串行接口的参数。使用IBERT核可以快速完成参数修改的任务,设置Loopback Mode在开环的模式下,TX Data Pattern为PRBS7-bit,调整摆幅、预加重参数,观察示波器上的信号眼图是否符合模板要求。图5和图6分别为调整摆幅预加重参数前后的眼图,图5所示眼图对应预加重0.8 dB、摆幅495 mV,眼图的眼高太小且图形碰撞模板,调整为预加重1.7 dB、摆幅1 180 mV,眼图满足的要求如图6所示。

为确定高速串行接口的参数是否满足硬件及多种环境的需求,可通过在对端器件高速串行接口设置远端环回,设置待测试芯片的收发data pattern为统一模式,常温及高低温拷机,观察误码率是否满足要求,误码率需满足E-10。例中与图6对应的参数值条件下,对端器件高速串行接口设置远端环回误码率为4.36E-10,满足误码率要求。

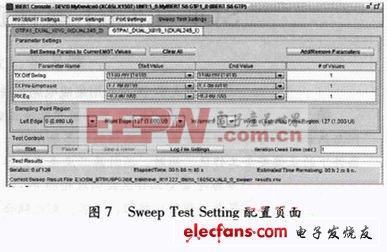

Sweep Test Setting(扫描测试)其配置页面如图7所示,以Rx Sampling Point来进行误码率测试定性分析信道质量为例,较为容易理解,当同定在某个采样点进行误码测试时,误码率达到E-10时,可判定信道质量良好。在整个UI范围内进行采样点的扫描测试时,误码率达到E-10的采样点越多,信号眼图的眼睛张得越大,距离模板的余量越大,信道质量越好。

3 结束语

通过以上实例,可见IBERT具有可操作性较强的GUI图形界面,可操作性强、准确、易用,可方便地设置高速串行收发通道的各项参数,并提供了多种环回模式及多种测试激励源,并可通过自动扫描测试,确定收发的最佳参数。可以满足硬件测试时对高速串行收发通道信号测试的大部分需求,在故障定位等场合均可使用。在单板的硬件测试初期,使用IBERT可以辅助硬件测试,例如设置发送通道的各项参数,协助示波器测量信号质量,而完全不需额外的开发FPGA逻辑。进行误码率测试,作为定量测量眼图质量、jitter等指标的补充。从示波器看图确定出的参数并非就是最佳参数。如示波器对于均衡后的信号质量无法测试,而通过IBERT测误码率能够测试到均衡之后的节点,测试范围更大。可以预见,集成比特误码测试仪IBERT将在FPGA设计中获得广泛应用。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)