低功耗10位100 MHz流水线A/D转换器设计

3 性能结果与分析

本文利用运放共享技术设计了一个10位100 MHz的流水线ADC,该ADC的最前端是一个输入带宽很大的采样保持电路,之后的8级MDAC输出利用运放共享技术使用了4个运算放大器,产生16位数字输出。最后一级为一个2位的FLASH模/数转换器。最终产生的18位输出经延迟对准后输入数字修正电路得到最后的10位数字编码。

本设计采用的是TSMC 0.18μm,混合信号1P6MCMOS工艺模型,提供MIM(metal-insulator-metal)结构电容,采用电源电压为1.8 V。使用Spectre进行验证。结果可得在100 MHz采样频率下,采用电容缩放技术后整个ADC电路的功耗为45 mW。

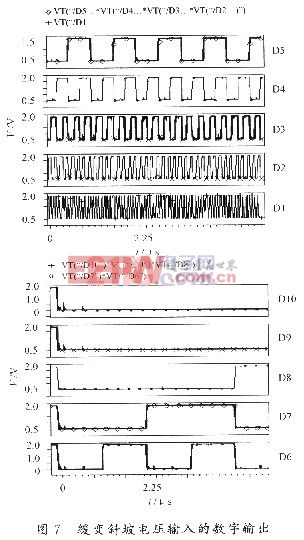

首先输入一个缓变斜坡电压进入模/数转换器,斜坡的变化时间和电路仿真时间必须保证ADC能够每个周期输出增加1位,也就是至少需要1 024个周期。图7为输入斜坡电压后,得到的10个数字码的输出情况。缓变的斜坡电压输入会使得输出每次按照递变的顺序变化,而从图5~图9中可以很明显地看到任意相邻的2个数字码都是按照00-01-10-11的顺序递变。通过观察所有的1 024个数字输出码,未发现任何误码和失码的情况。

图8所示为输入信号为10 MHz(奈奎斯特频率),采样频率100 MHz,采样点数为4 096时的数字输出经Matlab进行傅里叶变换的频谱结果输出,由图可知,SNDR=58.4 dB,SFDR=79.6 dB,此时ENOB=9.5位。

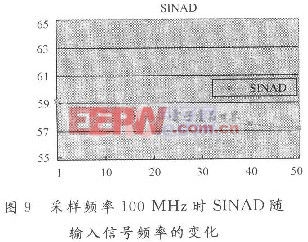

图9所示为采样频率100MHz时SINAD随输入信号频率的变化曲线。可见,在整个奈奎斯特频率内,电路均能达到9位以上的有效精度。ADC各项性能参数如表2所示。

4 结语

本文设计了一个10位100 MHz的低功耗流水线ADC电路。该ADC采用了相邻两级共用一个运放的运放共享技术和逐级电容缩减技术来减小功耗和面积。在输入频率达到奈奎斯特频率范围内,整个ADC的有效位数始终高于9位。在100 MHz采样频率下,电路的功耗仅为45 mW。

- 电子计价秤抗静电放电问题分析(04-25)

- A/D转换器THS1206在红外成像系统中的应用(12-07)

- 8通道24位△-∑型A/D转换器ADS1216的原理及应用(08-11)

- 宽带数字接收机的研究及实现(09-22)

- 可穿戴设备要流行,全方位高效电源管理是前提(12-09)

- 基于BQ25504的低功耗、增压型转换器的设计研究(12-09)