A/D转换器THS1206在红外成像系统中的应用

摘要:本文介绍了一款高速率、高精度、基于流水线结构的A/D转换芯片THS1206;并基于红外成像系统,详细介绍了该款芯片的基本结构、主要特点、应用要点及软硬件设计方案。实际测试表明,THS1206较好地实现了红外成像系统的数据采集功能。

关键词:A/D转换器;流水线结构;红外成像系统;高数据率

引言

THS1206是TI公司开发的一款基于流水线结构的12位高速A/D转换器。目前,A/D转换器主要有积分型、逐次比较型、并/串比较型、∑-△型和闪烁型等。闪烁型速率较高,但是分辨率一般只有8位左右;∑-△型转换精度高,但是速率较慢。为了兼顾转换速率和高精度的要求,出现了基于流水线结构的A/D转换器。这种A/D转换器采用流水线(pipeline)结构,能够并行处理多路模拟信号,因而可以得到较高的转换速度;并且可以通过其内部的校正电路对内部误差进行校正,得到更高的精度。

1 THS1206简介

1.1 THS1206特点及内部结构

THS1206因其高转换速度、高精度的特点,广泛应用于雷达、通信、高速DSP处理前端、控制应用等领域。它的主要特点有:

◆A/D转换速率高,最高可达6 Msps;

◆多通道可选输入,4路单端同时输入,或同时2路差分输入;

◆内部集成16字深度,12位的环形FIFO,可实现高速数据输出;

◆增强的工作温度范围,可达-55~125℃;

◆在2 MHz的工作频率下,信噪比可达68 dB;

◆具有自动检测模式;

◆3 V或5 V供电电压,功耗最大仅为216 mW。

THS1206由采样保持器、逻辑控制单元、12位流水线A/D采样单元、环形FIFO、控制寄存器、内部缓存单元组成,其内部结构如图1所示。

控制总线的输入/输出状态。当总线处于输入状态时,可以向芯片内部写入功能寄存器值。其中,总线高2位为寄存器地址,低10位为功能寄存器值。另外,芯片具有回读功能,可将控制寄存器设置的参数值回读。

控制寄存器的定义如表1所列。

其主要的控制寄存器说明如下:

①VREF:参考电压选择,0为内部参考电压,1为外部参考电压;

②MODE:模式选择,0为连续转换模式,1为单独转换模式;

③CHSEL0、CHSEL1、DIFF0、DIF1:通道和差分模式选择;

④OVFL/FRST:FIFO溢出标志位或FIFO复位控制;

⑤TRIG0、TRIG1:环形FIFO深度设置;

⑥DATA_T、DATA_P:中断信号DATA极性控制;

⑦RBACK:控制寄存器参数回读使能位。

1.3 环形FIFO

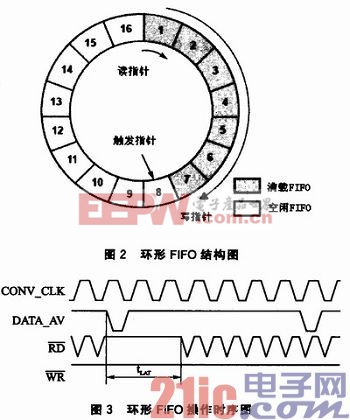

THS1206内部集成一个12位,最大深度为16的环形FIFO,用于实现与处理器的高速数据链接。该FIFO为一个可编程环形存储器,可以缓存内部转换后的数据,允许数据的写溢出。环形FIFO的结构图如图2所示。

数据根据芯片采集通道设置的不同,自动将数据按顺序写入FIFO中;读、写和触发指针控制了数据的写入和读出过程。首先,通过控制寄存器,设置FIFO的写入深度;当FIFO内数据到达写入深度后,中断信号DATA_AV有效,此时外部控制器需要及时将数据读出。需要注意的是,在实际设计中,经常会因为读写时序关系,导致数据采集失败。时序如图3所示。

该设计采样时钟CONV_CLK为6 MHz,触发深度为8。由于系统设计原因(例如PCB走线延时、处理器内部路径延时等),触发信号有效到开始读出数据迟滞的时间较长(tLAT),致使FIFO数据尚未完全读出时,处理器又向FIFO中写入新的数据,结果数据溢出,数据采集系统不能正确采集数据。因此,在设计中,应保证在中断信号有效时,将FIFO中数据及时读出。

2 红外成像系统

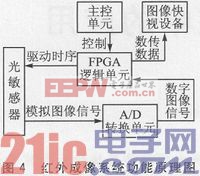

该红外成像系统由光敏感器、FPGA逻辑单元、主控单元和A/D转换单元组成。功能原理图如图4所示。

光敏感器选用Indigo公司的基于碲铬汞结构的ISC0002系列红外面阵探测器。该探测器像元分辨率为640×512,像元尺寸25μm×25μm,最大输出像元速率10 MHz。该探测器分两路输出图像数据,数据率为2 MHz,可将各转换后的像元图像信息电压输出。FPGA逻辑单元选用Xil inx公司的FPGA芯片XCV300,该芯片包含30万门逻辑资源,为光敏感器提供驱动时序,并与主控制器通信,实现各控制功能;A/D转换单元使用了一片THS1206,将红外探测器的两路模拟图像信号转换为数字信号,返回FPGA逻辑单元;最后,FPGA逻辑单元将数据打包整合,输出至图像快视设备,显示图像。

3 THS1206硬件设计

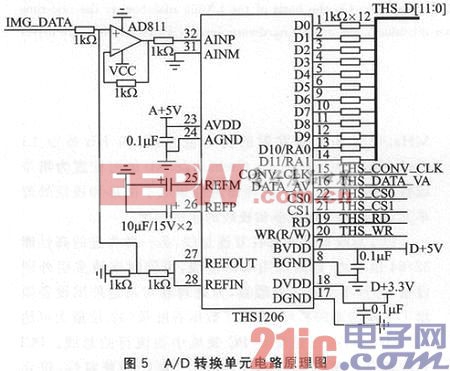

THS1206可以方便地和FPGA等处理器进行无缝连接。图5为红外成像系统A/D转换单元电路原理图。

THS1206外围配置电路简单,主要功能在芯片内部实现。只需要将各控制信号引脚输出至FPGA芯片,实现其控制即可。

在信号输人实现上,由于其输入电压范围为1.5~3.5 V,若输入信号不在此范围内,需要对输入信号进行电位的平移。本部分硬件设计采用了TI公司的推荐电路,利用电平移动放大器,将输入信号转换为1.5~3.5 V的电压信号后,再送入THS1206进行A/D转换。

4 软件设计

软件设计是实现高速数据采集的关键。如何合理使用其双向数据总线,实现芯片的初始化复位、状态设置、芯片中断响应、数据输出、数据回读,是设计中的难点所在。该系统软件基于FPGA平台,采用VHDL语言进行软件设计,程序流程图如图6所示。

A/D转换器 流水线结构 红外成像系统 高数据率 相关文章:

- 电子计价秤抗静电放电问题分析(04-25)

- 8通道24位△-∑型A/D转换器ADS1216的原理及应用(08-11)

- 低功耗10位100 MHz流水线A/D转换器设计(11-16)

- 宽带数字接收机的研究及实现(09-22)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)