一种12位50 MS/s CMOS流水线A/D转换器

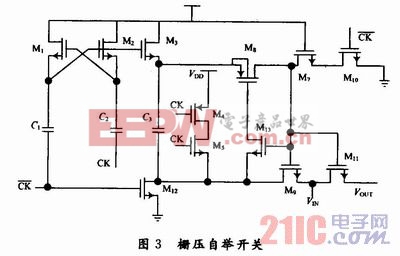

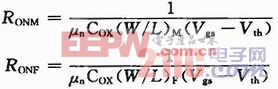

本文使用的Bootstrapped开关作为输入开关。这种开关在导通时可以保持导通电阻恒定,这样,因为开关导通电阻与输入信号相关而造成的非线性会被大大降低。具体电路如图3所示。M1,M2,C1,C2组成电荷泵,使M3的栅极与低电平为VDD,高电平为2VDD的方波信号相连。在CK为低电平时,M3和M12同时导通,使电容C2充电至电源电压。此时M10,M7导通,M11的栅极通过M7和M10与地相连,M11处于断开状态。当CK为高电平时,M10,M3,M12断开,M8,M9导通,这样,C3上的电压加到M11的栅源两端。可见在CK为高电平时M11的栅源电压一直固定在VDD,与输入信号无关。对于Sub ADC与MDAC,输入开关的导通电阻可以分别表示为:

由于Bootsrapped开关在导通时,开关管的栅源电压保持在VDD,因此开关的导通电阻只与开关管的尺寸有关。这样开关导通电阻因与输入信号相关而产生的非线性就被大大降低。

为了保持两条信号通路的时间常数(τ=RC)一致,有:

于是,MDAC与Sub ADC的采样开关的尺寸应该满足:

式中:RONM,RONF,CS,Cc分别指MDAC与Sub ADC的采样开关的导通电阻和采样电容;(W/L)M,(W/L)M分别指MDAC与Sub ADC的开关管的尺寸。

2.2 运算放大器

运算放大器是流水线ADC中最重要的单元模块,其消耗了整个ADC的大部分功耗。为了避免运放有限增益与带宽对ADC的转换精度产生影响,运放的开环增益和单位增益带宽必须满足:

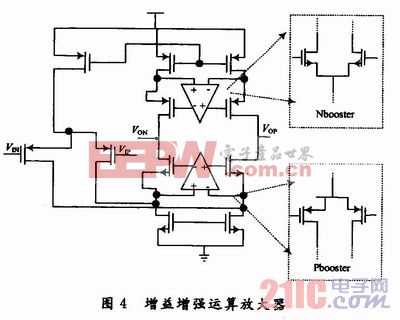

设计的运放如图4所示。主运放采用折叠式结构以扩大输出摆幅。自举放大器商样是两个折叠式放大器,其输入管分别采用PMOS管与NMOS管输入。这样主运放中靠近电源与地的晶体管只需一个过驱动电压大小的压降,这可以避免辅助运放限制主运放的输出摆幅。辅助运算放大器可以显著提升运算放大器的整体增益,但是它会与主运放形成局部反馈环路。该环路会在传输函数中引入零极点对。零极点对会延长运算放大器的建立时间。

为了避免零极点对的影响,应该使辅助运放的单位增益带宽(Waux)满足:

式中:Wc为主放大器构成的反馈环路的环路单位增益带宽;Wp2为主放大器构成的反馈环路的非主极点频率。

考虑到辅助运放的负载电容较小,可以使用较小的驱动电流。设计中,取辅助运放是主运放电流的1/8。整体运放使用开关电容共模反馈稳定输出共模电压。表1列出了第1级使用的运算放大器的几个主要参数,其余运放根据所在级的等效负载电容按比例减小偏置电流。

2.3 比较器

使用数字校正技术可以放宽对比较器失调电压的要求,简化比较器的设计。设计的比较器由3级组成:预防大级,重建锁存器和输出级,如图5所示。使用预防大级,可以减小传输延时。由于预放大器的增益不需要很大,使用40μA的尾电流,这样可以减小整个比较器的静态功耗。在CLK为高时,输出端箍位于阈值附近,在CLK变为低后,重建锁存器形成正反馈环路,将预放大级输出的电压差不断放大,直至将输出分别拉到电源和地。输出级采用反相器,提升比较器的驱动能力与避免亚稳态效应。

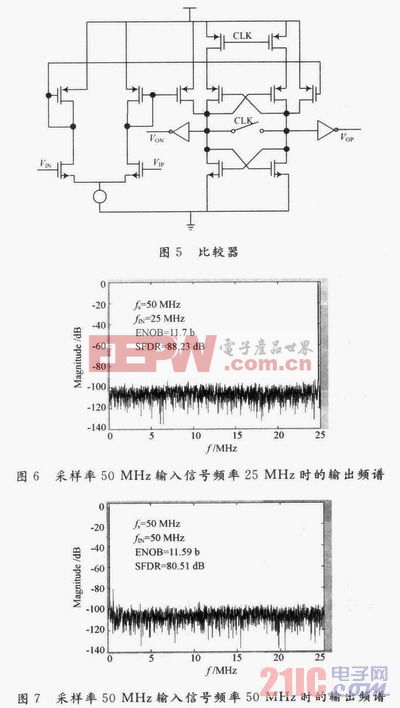

为了验证ADC的性能,在ADC的输入端加入单一频率的正弦波,并对输出波形进行傅里叶分析。图6是采样频率是50 MHz,输入25 MHz正弦波时的输出频谱图。此时电路的SNDR=72.19 dB,SFDR=88.23 dB,对应ENOB=11.70 b。图7是输入50MHz正弦波时,输出信号的频谱图,此时电路的SNDR=71.59,SFDR=80.51 dB对应ENOB=11.59 b。可见,通过取消SHA和匹配ADC的两条通道的时间常数,在输入低频和高频信号时ADC始终具有较好的线性度。在采样频率时50 MHz时,ADC的功耗为128 mW(不含参考电压产生电路)。表2列出了ADC的主要性能参数。

设计了一个12位50 MS/s的流水线ADC,该电路使用0.18μm 1P6M工艺实现。通过取消前端采样保持电路,消除了采样保持电路引起的失真和带来的功耗开销;经过仔细匹配输入时间常数,保证ADC在输入高频信号时依然保持足够线性度;使用运放缩减技术,进一步辟低了功耗。仿真结果表明,该ADC满足设计要求。

- A/D转换器THS1206在红外成像系统中的应用(12-07)

- 一种可重构流水线ADC的设计(07-17)

- 流水线ADC的行为级仿真(06-11)

- 1200V CoolSiCTM MOSFET兼具高性能与高可靠性(06-28)

- 如何借用同步整流架构提高电源转换器效率(12-09)

- 高端准谐振零压开关反激式转换器中的ESBT技术(12-09)