一种可重构流水线ADC的设计

摘要:对多标准无线通信系统中的A/D转换器进行了研究,根据无线通信系统的特点,构建了一个新型可重构流水线A/D转换器结构,该A/D转换器的可重构功能是通过在低分辨率下关断子级流水线来实现的。转换器的系统指标为6~14 b,从而可以在保证不影响ADC性能的前提下,引入新颖的可重构控制以进一步降低功耗。最后对改进的可重构流水线ADC进行了性能仿真。

关键词:多标准无线通信系统;流水线A/D转换器;可重构控制;性能仿真

随着无线通信技术的快速发展,各种无线通信标准正在往更高数据传输率的方向发展,同时对数据传输质量的要求也越来越高,以便提供更多更好的服务。所以随着无线通信技术的发展,无线终端对数据传输速率和质量的要求更高,对ADC的速度、精度也就提出更高的要求。同时随着无线通信协议的快速发展,多种不同的协议标准的共存变得不可避免,它们允许的输入信号频率范围、带宽、动态范围等都存在着很大的不同,因此这些协议所需要模/数转换器的工作模式也是不一样的。本文通过对无线通信系统中A/D转换器的可重构技术的研究,使其能够改变系统工作模式,达到降低设备功耗,提高数据处理速度,减少成本和设备模块的目的,该课题具有一定的研究价值。

1 无线通信系统的A/D转换器设计

1.1 多种无线标准系统的A/D转换器指标要求

本文研究的无线通信系统A/D转换器的指标要求如表1所示。可以看出无线终端中的A/D转换器性能需求包括分辨率在6~14位之间,采样速率在10~300 MS/s之间。未来的通信系统将能提供多种服务的集成,所以除了更高的数据传输速率外,多种服务的集合也是多标准无线终端的一个重要特性。

1.2 流水线ADC逐级Scaling down技术

当前出于低功耗设计的需要,逐级Scaling down设计技术目前得到了广泛的研究。流水线ADC逐级Scaling down主要包括各级采样电容取值的逐级缩减以及各级MDAC中OTA运放参数的缩减,为了便于本文核心观点的论述,对于各级采样电容的取值以及OTA运放的关键参数,本文采用文献所建议的优化值。同时相应列出文献提供的各级流水线的功耗,如表2所示。

1.3 可重构流水线A/D转换器的设计

基于对现有的适用于多标准无线终端的ADC结构的分析,并且当各级流水线通过逐级Scaling down设计的时候,前级相比后级消耗更大比例的功耗,所以在较低分辨率工作模式下,将前级流水线进行Poweroff的方法,可以较有效地降低功耗。为此引入一种新颖的可重构控制方法,提出了一种通过关断前级流水线的方法来降低功耗的可重构ADC结构。可重构流水线ADC的整体结构如图1所示。

由图1可知:改进的可重构流水线ADC包括一个可重构控制器、5个分辨率位数重构控制开关即K1~K5、采样保持电路、13级可控的1.5位/级的流水线级、延时对齐电路和数字校正电路。各级流水线的工作状态受重构控制器的控制。Fr为来自系统的高层,即MAC层或者其他仲裁器的重构控制信号。Vin为输入的模拟信号。由图1可知改进的可重构流水线ADC是在14位1.5位/级流水线ADC结构的基础上,引入可重构控制,可以实现:分辨率位数为6,8,10,12,14位的动态可变;各相应未参与贡献分辨率的流水线级可进行关断,进入休眠模式,节省功耗。

1.3.1 可重构控制器结构

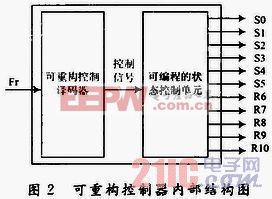

可重构控制器内部结构图如图2所示,它包括:重构控制器电路由重构控制译码器电路和逻辑状态可编程的状态控制单元组成。对于设计中,有S0~S5及R6~R10共计11个状态控制信号。可以看出,这是一个简单的数字逻辑控制电路,容易实现。

1.3.2 可重构流水线ADC工作原理

整个可重构流水线ADC的工作原理如下:首先,系统将重构控制信号即Fr送给可重构控制器,重构控制器内部的可重构控制译码器,对可重构控制信号进行译码,并对状态控制单元进行编程,即对其信号状态进行刷新,本文中,为了以减少控制信号,出于低功耗设计的需要,尽量降低额外电路附加的功耗,在逐级Scalingdown设计技术目前得到了广泛的研究和运用情况下,所以对电路实现6/8/10/12/14位数字输出。对于流水线一、二级,三、四级,五、六级,七、八级在各种模式下都是一起工作的,所以分别用一个控制信号来实现控制,并且ADC至少需要6位的分辨率输出,所以后面五级流水线,即第九级到第十三级,也用一个控制信号来对这五级流水线进行控制。另外,可重构控制器可以响应系统高层的控制,而对于系统根据工作环境的不同,相应在不同工作模式下进行切换的检测控制算法和控制决策,则由系统高层,即MAC层或者其他仲裁器完成,而不作为重构控制器的任务。因为控制决策用软件实现相比硬件具有更大的灵活性,而不至于使得硬件电路过于复杂,并且通过软件的方法能够提供用户自己可以根据需要进行自定义操作,这一点正是可重构电路系统的优势所在。

1.4 可重构流水线功耗分析

整个流水线ADC功耗组成为:各1.5位/级流水线级消耗的功耗和,采样保持电路消耗的功耗,可重构控制所消耗的功耗数字校正电路消耗的功耗。由于采用不同的工艺,不同的设计者,设计出来的电路会不同,功耗也不一样。表2所示的各级流水线的功耗估计值,只是一个大致的参考估计值,但是各模块之间的功耗比例是有意义的。本文对各模块确切的功耗值不做深入分析,可以假设除各级流水线及采样保持电路外,其余电路的功耗为首级流水线功耗减去S/H部分的功耗,基于各模块之间的功耗比例,可以大致推算出,五种不同工作模式下的功耗比例如表3所示。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)