1200V CoolSiCTM MOSFET兼具高性能与高可靠性

作者 Marc Buschkühle 英飞凌科技股份公司

摘要:SiC在电源转换器的尺寸、重量和/或能效等方面具有优势。当然,要进行大批量生产,逆变器除了静态和动态性能之外,还必须具备适当的可靠性,以及足够的阈值电压和以应用为导向的短路耐受能力等。可与IGBT兼容的VGS=15V导通驱动电压,以便从IGBT轻松改用SiC MOSFET解决方案。英飞凌的1200V CoolSiCTM MOSFET可满足这些要求。

引言

研发以T- MOSFET设计为辅的CoolSiC?,是为了抑制导通及关断状态下栅极氧化层内的电场。在1200V电压等级的导通电阻颇具吸引力,哪怕以稳定的可复制的方式进行大批量生产,也可以实现这样的导通电阻。已在VGS=15V驱动电压等级下实现的低导通电阻和超过4V的栅极-源极阈值电压,在SiC晶体管领域树立了标杆。必须满足这些限制条件,才可能将硅功率半导体领域成熟的质量保证措施转而用于SiC器件,以确保实现工业乃至汽车应用领域所要求的故障率(FIT)。

对于快速开关IGBT和SiC晶体管,封装设计同样重要。

当前市场上的功率模块平台中,有些封装非常有利于实现快速开关SiC器件。杂散电感必须尽可能低,此外还需要高度对称的设计。

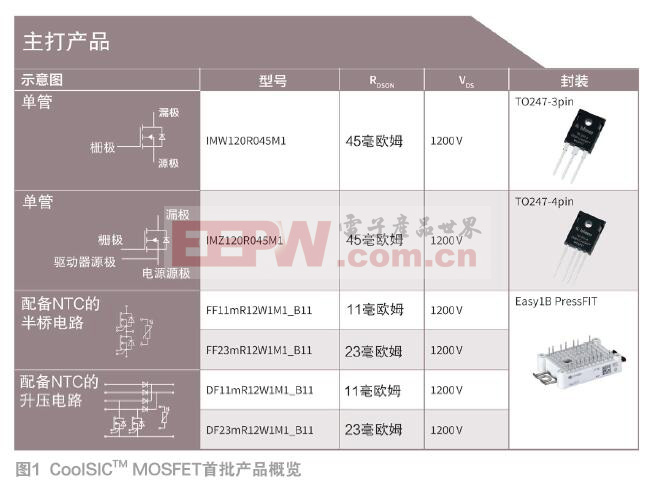

举例来讲,Easy-Module平台注定将用于SiC器件。与众所周知的基于衬底的标准封装不同,Easy-Module平台可以实现高度对称的低电感设计。为此,利用通用灵活的Easy1B功率模块, 实现了首批针对光伏系统、非车载充电器和不间断电源等应用而优化的SiC半桥和升压器解决方案。

Easy模块的灵活针栅可简化电路板布局,实现低于10 nH的杂散电感。这是一个巨大的进步,较之诸如EconoDUAL?等现有解决方案或标准SIXPACK设计,降低70%~80%。它代表着功率模块设计领域的重大创新。

图1所示为首批产品概览。所列产品只是大批量优化型CoolSiC? MOSFET系列的首批产品,还有更多器件目前正在开发之中。

器件设计理念

SiC MOSFET的开关损耗通常很低,并且几乎不受温度影响。高级设计工作者将单位面积导通电阻作为特定技术的主要基准参数。对于基于4H-SiC的平面MOSFET,必须克服导带附近的超高界面陷阱密度。这会导致很低通道迁移率,从而使通道电阻占总导通电阻的很大比重。形形色色的基于SiC MOSFET的器件,都存在很高缺陷密度。经验表明,克服这一困境的方法是提高导通状态下施加在氧化层上的电场强度,达到高于硅基MOSFET器件的典型值。导通状态下,氧化层内的高电场有可能加剧老化。这可能危及长期可靠性,特别是就SiC衬底的高缺陷密度而言。

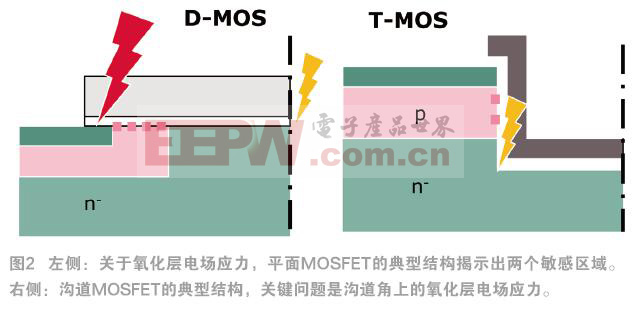

根据这些考量,显然就氧化层电场应力而言,采用SiC技术的平面MOSFET器件事实上有两个敏感区域,如图2左侧所示。

首先,通常讨论的是,漂移区与栅极氧化层间界面附近的最高电场区域内的反向模式下的应力,其次是栅极与源极之间的重叠区域内的导通状态下的应力。

导通状态下的高电场更为危险,因为器件设计未采取任何措施来降低导通状态下的电场应力。因此,总体目标是器件既要利用SiC技术实现很低的RDSon,又要采用仍能实现经深入研究的安全的氧化层场强状态的运行模式。在导通状态下,通过从存在高缺陷密度的平面表面,改为其他更有利的表面定向,可以实现这一点。

栅极氧化层可靠性

关于SiC MOS器件的栅极氧化层可靠性,挑战是确保在设计使用寿命期限内和特定运行条件下,实现足够低的故障率,包括非本征缺陷。典型行业要求为20年运行期内低于100 ppm。SiC MOS器件栅极氧化层的非本征缺陷的根源主要在于衬底材料和外延工艺的缺陷,另外,其余工艺过程也有一些影响。对商用MOSFET产品进行的试验显示,对于工业系统的应用,这个问题依然十分严峻。

因此,采用大量器件进行了长期试验,以研究英飞凌CoolSiC? MOSFET的栅极氧化层非本征故障率。试验采用两组每组各1000个单管器件进行,在150℃和恒定栅偏应力下进行测试,连续执行三个100天。图3总结了试验结果。每隔100天,栅源电压增加+5 V。

这些统计数据非常符合线性E-Model。确定了与图3内的实线最吻合的加速系数。

根据这一结果,对器件以推荐电压等级运行20年进行推算,模型预测出故障率为0.2 ppm。因此,这个证据表明,其栅极氧化层的可靠性与IGBT类似,完全满足典型工业要求。

图3长期试验:图3中所示为故障次数随应力天数的变化。试验采用两组每组各1000个单管器件进行,试验条件为150℃和恒定栅极电压VGS,如图3所示。每隔100天,VGS增加5V。每个点表示一次故障。实线代表线性E模型的预测。

动态性能

作为单极器件,SiC MOSFET的动态性能主要取决于其电容。该器件经专门设计,相比于输入电容Ciss,其栅极漏极反向电容Crss很小。这有利于防止MOSFET在半桥模式下运行时,形成寄生导通效应和复杂的栅极驱动电路。

下一篇:??????????????????????????????????????? ???????????????????????????????????????????????????????????????

电源转换器 SiC MOSFET 逆变器 201707 相关文章:

- 如何借用同步整流架构提高电源转换器效率(12-09)

- 汽车电源转换器的选购指南(12-08)

- 开关电源转换器电力电子集成技术分析(01-07)

- 新型电源转换器与稳压电源(01-07)

- 基于能量循环的电源节能方案(12-11)

- TPS62120—高效率电源转换器的特性与优点(11-18)