基于Verilog HDL滤波器的设计

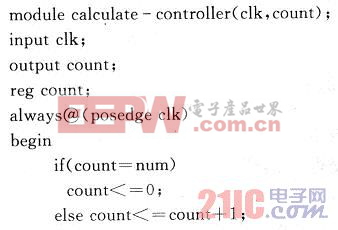

寄存器移位,累加器的循环周期和计算输出,并控制移位寄存器的数据输入。 2 利用VerilogHDL语言实现以上功能 2.1 用VerilogHDL语言进行算法建模 计算机控制器的veril—ogHDL模型: 寄存器组中每个寄存器的位数为0,1,…,num一1。 2.2 定制ROM QuartusⅡ包含有许多有用的LPM模块,它们是复杂或高级系统构建的重要组成部分,可以与QuartusⅡ普通设计文件一起使用,该文使用“Tools”菜单下的MegaWizardPlug—In Manager命令定制ROM的元件。如图5所示。 2.3 用VerilogHDL进行数据流建模 滤波器的建模过程如下: 3 验证仿真 利用Altera公司的QuartusⅡ7.2软件内部带有仿真器对滤波器的VerilogHDL模型进行波形仿真,通过建立正确的Vector Waveform File就可以开始仿真了。如图6所示。 通过QuartusⅡ的波形仿真功能,对输入输出进行波形仿真,对其结果进行定量分析。通过时序分析和功能分析结果,对设计进行进一步的完善。在仿真中,in—put滤波器输入数据,output滤波器输入数据x0,x1,x2,x3,x4为移位寄存器组中寄存器,count为控制计数器,table-in为流水线寄存器。所得结果如图6所示。经验证,仿真结果和实际运算结果一致。所以对于大多数连续的LTI系统都可以采用以上方法进行分析,但是他也有局限性:对于时变系统,非线性系统分析,它无能为力;只适合分析一维变量,对于多维变量,它无能为力;可采用状态变量分析方法;就精确度来说,这种分析方法不是很高。 尽管连续LTI系统有很多缺点,但是通过对LTI系统的分析可以培养系统建模和求解能力,为以后分析其他系统作参考。

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)