基于Verilog HDL滤波器的设计

现代计算机和通信系统中广泛采用数字信号处理的技术和方法,其基本思路是先把信号用一系列的数字来表示,然后对这些数字信号进行各种快速的数学运算。其目的是多种多样的,有的是为了加密,有的是为了去掉噪声等无关的信息,称为滤波;有时也把某些种类的数字信号处理运算成为变换,如离散的傅里叶变换,小波变换等。VerilogHDL是目前应用最广泛的一种硬件描述语言,用于数字电子系统的设计。可用它进行各种级别的逻辑设计,并进行数字逻辑系统的仿真验证,时序分析,逻辑综合。小波滤波器的设计属于复杂算法的电路设计,因此利用Veril—ogHDL对双正交小波滤波器进行建模、仿真,实现电路的自动化设计,将是一种较为理想的方法。

Verilog HDL介绍

Verilog HDL是一种硬件描述语言,是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是目前世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司开发。两种HDL均为IEEE标准。

Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种硬件描述语言,它是由GDA公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得Verilog HDL迅速得到推广应用。1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。1990年CADENCE公司公开发表了Verilog HDL,并成立LVI组织以促进Verilog HDL成为IEEE标准,即IEEE Standard 1364-1995.

Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。与之相比,VHDL的学习要困难一些。但Verilog HDL较自由的语法,也容易造成初学者犯一些错误,这一点要注意。

l 小波滤波器的设计

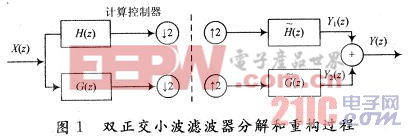

对于小波函数,要求它具有正交性、紧支集、对称性和平滑性。正交性可以使变换无冗余;紧支集则带来优良的空间分辨率;对称性保证了与其对应滤波器的相位为线性;平滑性可以产生较小的失真。这样使离散二进小波变换受到很大的限制,为此,人们提出一种双正交的小波变换。本文设计小波滤波器正是基于双正交小波变换的一种双通道完全重构滤波器,因此可以对信号进行分解后实现精确重构,所以对信号的滤波有很好的作用。由于它具有正变换二元上抽样采样和反变换二元下抽样采样特性,在进行滤波器设计时可以将双正交小波滤波器设计成具有多相结构的双通道完全重构滤波器。双正交小波变换可以看成原始信号通过一系列高低通滤波器滤波并经过抽样后所得到的结果,重构过程与此相反。为了使变换后的信号能够完全重建,须满足Y(n)=x-kX(n),在这里取k=1。双正交小波滤波器分解和重构过程如图1所示。

设G(z),H(z)分别为分解低通,高通滤波器,下采样后用H(z)滤波等价于先用H(z2)滤波,然后下采样,所以:

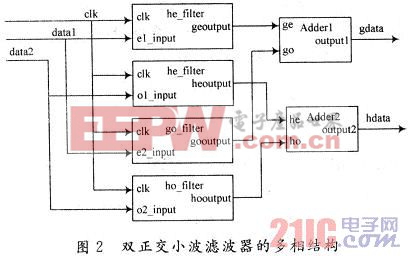

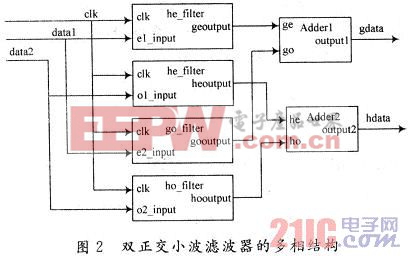

其中:Ge和Go分别是G(z)的偶数项和奇数项,He和H。分别是H(z)的偶数项和奇数项。根据式(1),式(2)可以建立双正交小波滤波器的多相结构模型如图2所示。

下面对双正交小波滤波器用VerilogHDL进行顶层设计:

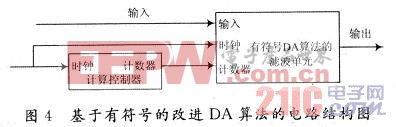

对于双正交小波滤波器的部件Ge,Go,He,Ho设计,采用行为描述方式进行设计。VerilogHDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL级的模型设计。在Veril—ogHDL语言中行为描述分为算法和RTL两种。算法级:用语言提供的高级结构能够实现算法的运行模型。RTL级:描述数据在寄存器之间的流动和如何处理,控制这些数据的流动,采用改进的DA算法(如图3所示)。DA算法完成一次滤波所需要B次的累加也就是B个时钟周期完成一次运算,B位输入数据的位宽。它的查找表(LUT)的大小是由滤波器的阶数N决定的,共需要2N个查找表单元,如果系数N过多,用单个LUT不能够执行全字查找则可把系数分组,利用部分表并将结果相加,为了简单的阐述算法,在此系数只分了2组,每个单元的位宽是由滤波器的系数的量化决定的。Ge,Go,He,Ho四个滤波器虽然长度不同,但具有相同的电路结构,如图4所示。

计算控制器用于控制滤波单元中移位

- 直接变频接收机设计可实现多标准/多频带运行(10-11)

- 基于蓝牙芯片的无线通信模块设计与开发(02-03)

- 无线通信网络设计与现场测试(10-10)

- WiMAX数据传输加密方案设计与实现(05-25)

- 高性能TD-SCDMA接收机的设计(03-15)

- 初步设计WiMAX射频系统(03-29)